# ELECTRONICS (DPHY04) (MSC PHYSICS)

## ACHARYA NAGARJUNA UNIVERSITY

## **CENTRE FOR DISTANCE EDUCATION**

NAGARJUNA NAGAR,

## GUNTUR

ANDHRA PRADESH

1

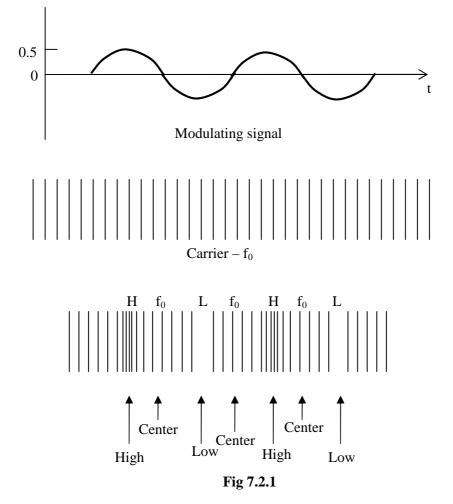

#### UNIT I:

#### **LESSON 1**

### **OPERATIONAL AMPLIFIERS I**

#### **Objectives:**

- ➤ to explain the basic differential amplifier

- Introducing the operational amplifier

- > To discuss the properties of operational amplifier.

#### **Structure of the lesson :**

- 1.1 Differential Amplifier

- 1.2 Operational amplifier

- 1.3 Properties of practical op-amp

- 1.4 Summary of the Lesson

- 1.5 Key terminology

- 1.6 Self-assessment questions

- 1.7 Reference Books

#### **1.1 Differential Amplifier**

The differential amplifier, also called a difference amplifier, as the name implies, amplifies the difference between two signals. Because of its balanced nature and symmetry, it can amplify very small signals. It usually requires a minimum number of capacitors and can operate without bypass and coupling capacitors. It is the basic building block of operational amplifiers, which are most widely used in integrated circuits.

Fig 1.1 Schematic diagram of a differential amplifier.

For a linear active device with two input signals v1 and v2 and the out put signals v0 each measured with respect to ground, we have

$$v_0 = A (v_1 - v_2) - (1.1)$$

where A is the voltage gain of the differential amplifier. In actual practice, the output depends not only upon the difference of the two input signals but also upon the average level. In symmetrical circuits we talk about the in-phase signals (called common mode (CM) Signals  $v_c$ ) and the difference or anti-phase signals (called differential mode (DM) signals  $v_d$ ). They are defined as

$$v_c = \frac{1}{2}(v_1+v_2)$$

, and  $v_d = (v_1 - v_2)$ -----(1.2)

The output v<sub>0</sub> can be expressed as linear combination of the two input voltages, as

$v_0 = A_1 v_1 + A_2 v_2 - \dots (1.3)$

Where  $A_1$  and  $A_2$  are the voltage amplifications from input 1 and 2 respectively. From equations (1.2) and (1.3) we get

$$v_{o} = A_{1}(v_{c} + \frac{1}{2}v_{d}) + A_{2}(v_{c} - \frac{1}{2}v_{d}) = (A_{1} + A_{2})v_{c} + \frac{1}{2}(A_{1} - A_{2})v_{d} = A_{c}v_{c} + A_{d}v_{d} - \dots - (1.4)$$

where  $A_c = A_1 + A_2$  and  $A_d = \frac{1}{2}(A_1 - A_2)$ , are voltage gains for the signals in common mode and differential modes respectively. They may be defined as

$$\mathbf{A}_{\mathrm{d}} = \left(\frac{\mathbf{v}_{0}}{\mathbf{v}_{d}}\right)_{\mathbf{v}_{\mathrm{c}}=0} \text{ and } \mathbf{A}_{\mathrm{c}} = \left(\frac{\mathbf{v}_{0}}{\mathbf{v}_{\mathrm{c}}}\right)_{\mathbf{v}_{\mathrm{d}}=0} -\dots -(1.5)$$

Thus  $A_d$  can be measured directly by setting  $v_c = 0$ , or  $v_2 = -v_1$ .

The  $A_c$  can be measured by setting  $v_d = 0$ , or  $v_2 = v_1$ , generally the desired signals in differential amplifier are DM and undesired signals are CM. The figure of merit for differential amplifier in defined as

$$\rho = \left[\frac{A_{d}}{A_{c}}\right] - \dots - (1.6)$$

This is called the common-mode rejection ratio (CMRR) and is also some times referred to as the discrimination factor of a differential amplifier. Ideally  $A_c=0$ , and CMRR=  $\infty$ . In practice, A/c is non-zero but very small, where as  $A_d$  is very large. The combination of equations (1.4) and (1.6) gives

$$Vo = A_{d} v_{d} \left[ 1 + \frac{A_{c} v_{c}}{A_{d} v_{d}} \right] = A_{d} v_{d} \left[ 1 + \frac{v_{c}}{v_{d}} \cdot \frac{1}{CMRR} \right]$$

$$V_{0} = A_{d} v_{d} \quad (since CMRR = \infty) \qquad -----(1.7)$$

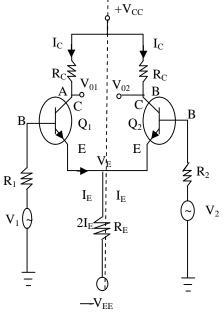

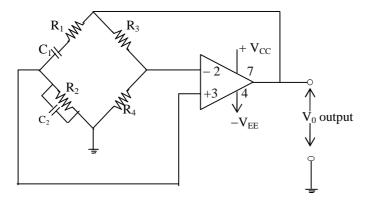

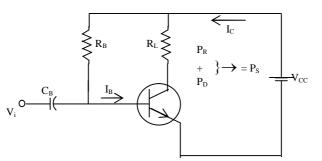

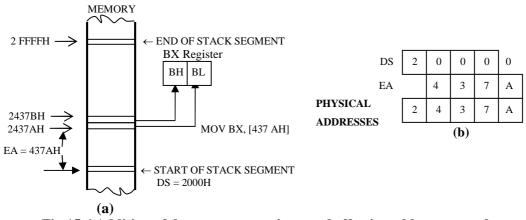

A basic differential amplifier circuit (ckt), consisting of two interlocked common emitter amplifier stages is shown in fig (1.2). The two stages are linked by having both emitters connected to a constant current generator. As current through one emitter increases, current through the other decreases. The circuit is symmetric about the vertical dashed line and the two transistors and resistors  $R_c$  form a bridge circuit that is balanced under zero input signal. The resistors and the transistors are simultaneously fabricated in adjacent areas on a small chip. They will be at the same temperature. A simultaneous change in  $h_{FE}$  or  $v_{BE}$  will produce equal changes in the voltages at a and b and  $v_0$  will not be affected.

Fig (1.2) Basic differential amplifier circuit diagram

Consider the circuit operation with no input signals. For  $v_1=v_2=0$ , an emitter current  $I_E$  flows in each BJT. Therefore  $I_C = I_E$  and

$V_{01} = V_{02} = V_{CC} - I_C R_C$  ------(1.8) thus the base current  $I_B = \frac{I_E}{h_{FE}}$  ------(1.9) and  $V_E = -I_B R_1 - V_{BE}$  ------(1.10)

If v<sub>CE</sub> is chosen large enough to bias each BJT in the center or the linear operating region, then

$$V_{CC} = V_{EE} + 2 I_E R_E + V_{CE} + I_C R_C$$

------(1.11)

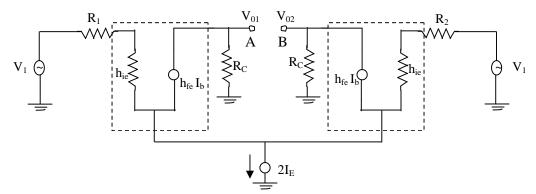

The ac equivalent circuit for use differential amplifier is shown in fig (1.3). Here it is assumed

3

| M    | . Sc. Physics | 4 | Opamp I |

|------|---------------|---|---------|

| H. 1 |               | 1 | Opump I |

$h_{oe} R_C \ll 1$  or  $h_{oe} \ll 1/R_C$  and thus  $h_{oe}$  is omitted in this figure. The collector current  $I_c = h_{fe} I_b$ . The voltage  $h_{re} v_c$  is neglected in comparison with the  $h_{ib} I_b$  drop across  $h_{ie}$

Fig (1.3) AC equivalent circuit of basic differential amplifier

Common mode voltage gain :

Let

$$v_1 = v_2 = v_s$$

, user  $A_c = \frac{v_o}{v_c} = \frac{v_o}{v_s}$ .

Due to symmetry, each input at the base, sees a common emitter circuit, with an un bypassed emitter resister of  $2R_E$  (the emitter resistor is effectively doubled, as it carries the emitter current for both transistors). Thus we have

$Z_i = R_1 + h_{ie} + 2R_E (1 + h_{fe}) \text{ and } Z_0 = R_c$  ------(1.12)

Current gain =

$$A_i = \frac{-I_c}{I_b} = \frac{-h_{fe} I_b}{I_b} = -h_{fe}$$

-----(1.13)

Voltage gain  $A_v = \frac{A_i Z_0}{Z_i} = \frac{-h_{fe} R_c}{(R_1 + h_{ie} + 2R_E(1 + h_{fe}))}$  -----(1.14)

Since usually  $(1+h_{fe}) 2R_E \gg h_{ie}$  and  $1+h_{fe} = h_{fe}$ . The source resistance  $R_i \ll h_{ie}$ . Therefore

$$A_v = \frac{-R_c}{2R_E}$$

= common mode voltage gain  $A_c$ .

Differential mode voltage gain:-

Let

$$-v_2 = v_1 = \frac{v_s}{2};$$

Acharya Nagarjuna University

5

)

Therefore  $v_d = v_1$ ,  $-v_2 = v_s$  and  $A_d = \frac{v_0}{v_d} = \frac{v_0}{v_s}$ . From the symmetry of fig(1.2) for  $v_1 = -v_2$ ,

the emitter of each transistor is grounded for small signal operation i.e  $R_E=0$  and

$$Z_{i} = 2(R_{i} + h_{ie}), Z_{o} \cong R_{c}, A_{i} \cong -h_{fe}. \qquad -----(1.15)$$

$$A_{v} = \frac{A_{i}Z_{0}}{Z_{i}} = \frac{-h_{fe}R_{c}}{2(R_{i} + h_{ie})} \qquad -----(1.16)$$

= differential mode voltage gain  $A_d$ .

#### Common mode rejection ratio:-

Thus we see that CMRR increases with  $R_E$  as desirable.

#### **Constant current generators:**

Instead of resistor  $R_E$ , a constant current generator is used. It may be a JFET with its gate tied to its source. A BJT can be used in a similar way with voltage divider bias. In both cases the output current is approximately constant as long as the voltage across the device is sufficient.

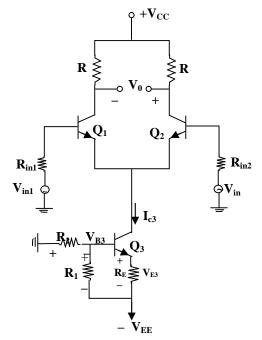

#### Constant current bias:-

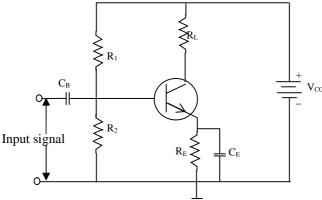

In the differential amplifier discussed so far, the combination of  $R_E \& V_{EE}$  is used to set up the dc emitter current. We can also use constant bias to set up the dc emitter current if desired. In fact the constant current bias is better because it provides current stabilization and in turn, assures a stable operating point for the differential amplifier. Fig(1.4). shows the dual input balanced output differential amplifier using a resistive constant current bias. Notice that the resistor  $R_E$  is replaced by a constant current source transistor (Q3) circuit. The dc collector current in the transistor  $Q_3$  is established by resisters  $R_1$ ,  $R_2$  and  $R_E$  and can be determined as follows. Applying the voltage divider rule, the voltage at the base of transistor  $Q_3$  (neglecting base loading effect) is

$$I_{C3} = v_{EE} - \left(\frac{-R_2 V_{EE}}{(R_1 + R2)}\right) \cdot \frac{V_{BE3}}{R_E} \quad -----(1.21)$$

Because two halves of the differential amplifier are symmetrical, each has half of current I<sub>ce3</sub>.

That is

The collector current  $I_{c3}$  in transistor  $Q_3$  is fixed and must be invariant because no signal is injected into either the emitter or the base of  $Q_3$ . Thus the transistor  $Q_3$  is a source of constant emitter current for transistors  $Q_1$  and  $Q_2$  of the differential amplifier. Besides supplying constant emitter current, the constant current bias also provides a very high source resistance since the ac equivalent of the dc current source is ideally an open circuit.

Fig (1.4) Differential amplifier using constant current bias.

#### **1.2 Operational amplifier:**

An operational amplifier is a direct-coupled high gain amplifier usually consists of one or more differential amplifiers and usually followed by a level translator and an output stage. The output

7

stage is generally a push pull or push pull complementary symmetry pair. An operational amplifier is available as a single integrated circuit package. The operational amplifier is a versatile device that can be used to amplify dc as well as ac input signals and was originally designed for computing such mathematical functions as addition, subtraction, multiplication and integration. Thus the name operational amplifier stems from its original use for doing these mathematical operations and so is abbreviated to op-amp. With the addition of suitable external feed back component the modern day operational amplifier can be used for a variety of applications. Such as ac and dc signal amplification, active filters, oscillators, comparators, regulators and others.

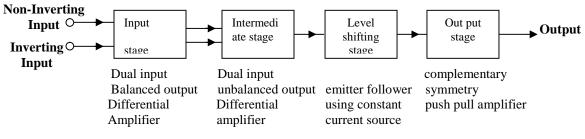

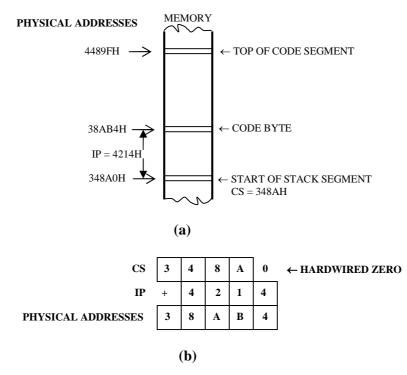

#### Block diagram representation of a typical op-amp:

Since an op-amp is a multistage amplifier. It can be represented by a block diagram shown in figure (1.5)

The input stage is the dual input balanced output differential amplifier. This stage generally provides most of the voltage gain of the amplifier and also establishes the input resistance of the op-amp. The intermediate stage is usually another differential amplifier, which is driven by the output of the first stage. In most amplifiers, the intermediate stage is dual input unbalanced (single ended) output. Because direct coupling is used, the dc voltage at the output of the intermediate stage is well above ground potential. Therefore, the level translator circuit is used after the intermediate stage to shift the dc level at the output of the intermediate stage downward to zero voltage with respect to ground. The final stage is usually a push pull complementary amplifier output stage. The output stage increases the output voltage swing and raises the current supplying capabilities of the op-amp. The well designed output stage also provides low output resistance.

Fig (1.5) Block diagram of a typical op-amp

Opamp l

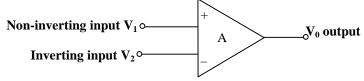

#### Schematic symbol:

The most widely used symbol for a circuit with two inputs and one out put is shown in fig (1.6)

Fig (1.6) Schematic symbol of op-amp

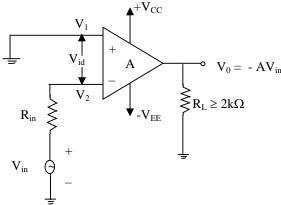

In fig (1.6)

$v_1$  = voltage at the non-inverting input (volts)

$v_2$  = voltage at the inverting input (volts)

$v_o = output voltage (voltage)$

All these are measured w.r.t. ground

A = large signal voltage gain that is specified on the data sheets for an op-amp

For amplifier, power supply and other pin connections are omitted. Since the input differential amplifier stage of the op-amp is designed to be operated in the differential mode, the differential inputs are designated by the (+) and (-) notations, the (+) input is used for non-inverting input. An ac signal (or dc voltage) applied to this input produces an in-phase (or same polarity) signal at the output. On the other hand the (-) input is the inverting input because an ac signal (or dc voltage) applied to this input produces an 180 out of phase (or opposite polarity) signal at the output.

#### Ideal op-amp:

An ideal op-amp exhibits the following electrical characteristics.

- (1) Infinite voltage gain  $A_V$ .

- (2) Infinite input resistance R<sub>i</sub>, so that, almost any signal source can drive it and there is no loading of the preceding stage.

- (3) Zero output resistance  $R_0$ , so that, output can drive an infinite number of other devices

- (4) Zero output voltage when the input voltage is zero.

- (5) Infinite bandwidth, so that, any frequency signal from 0 to  $\propto$  Hz can be amplified with out attenuation.

- (6) Infinite common mode rejection ratio so that output common mode noise voltage is zero.

9

(7) Infinite slew rate so that voltage changes occur simultaneously with input voltage changes.

There are practical op-amps that can be made to achieve some of these characteristic using a negative feedback arrangement. In particular, the input resistance, the output resistance, and bandwidth can be brought close to ideal values by this method.

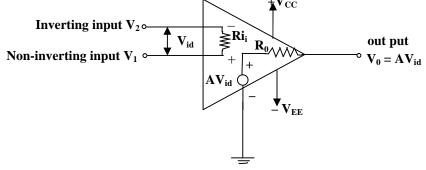

**Equivalent circuit of an op-amp:** Fig (1.7) shows an equivalent circuit of an op-amp. The circuit includes important values from the data sheets: A,  $R_i$  and  $R_o$ .

Note that A  $v_{id}$  is an equivalent Thevenin voltage source, and  $R_o$  is the Thevenin equivalent resistance looking back into the output terminal of an op-amp.

Fig (1.7) Equivalent circuit of op-amp

The equivalent circuit is useful in analyzing the basic operating principles of op-amps and in observing the effectiveness of feed back arrangement. For the circuit shown in fig (1.7), the output voltage is

$v_0 = Av_{id} = A(v_1 - v_2)$  -----(1.23)

Where A = large- signal voltage gain

$v_{id}$  = difference input voltage

$v_1$  = voltage at the non-inverting input terminal w.r.t. ground.

$v_2$  = voltage at the inverting input terminal w.r.t. ground.

Eqn.(1.23) indicates that the output voltage  $v_0$  is directly proportional to the algebraic difference between the two input voltages. In other words the op-amp amplifies the difference between the two input voltages; it does not amplify the input signal voltages themselves. For this reason the polarity of the output voltage depends upon the polarity of the difference voltage.

| M. Sc. Physics | 10 | Opamp I |  |

|----------------|----|---------|--|

|                |    |         |  |

#### **1.3 Properties of practical op-amp:**

To enhance our understanding of op-amps, we need to define some parameters that appear on data sheet of practical op-amp.

#### (1) Voltage gain:

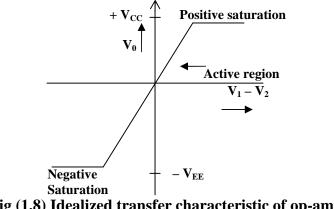

Fig (1.8) shows an idealized transfer characteristic

In the active region the slope of the curve is the differential mode voltage gain Ad is defined as

$A_d = \frac{\Delta v_0}{\Delta v_1}$ , where  $v_d = v_1 - v_2$ , the differential mode input.  $A_d$  is very large ~ 10<sup>6</sup>.

Fig (1.8) Idealized transfer characteristic of op-amp

To stabilize the voltage gain, negative feedback is always used. Fig (1.8) shows that the voltage gain is virtually zero when the output is at saturation level.

#### (2) Input impedance R<sub>i</sub>:

It is the open loop incremental impedance looking into the two input terminals. It is large  $(\sim M \Omega)$

#### (3) Output impedance R<sub>0</sub>:

It is the open loop impedance across the output. It is low (~  $100 \Omega$ )

#### (4) ): Common mode rejection ratio (CMRR):

The op-amp should ideally respond to a difference mode only. There will also be an output for the common mode input, because of the nature of the input circuit any (differential

amplifier). The common mode gain  $A_c = \frac{\Delta v_0}{\Delta v_c}$

The ratio of these two gains is defined as common mode rejection ratio

$$CMRR = \left| \frac{A_{d}}{A_{c}} \right| \qquad (1.24)$$

It is usually expressed in decibels, as  $20 \log_{10} (CMRR) = 20 \log_{10} |A_d| - 20 \log_{10} |A_c|$ It is having a value 70 dB to 100 dB

Op-amps are further classified into two groups: general- purpose and special purpose. General- purpose op-amps may be used for a variety of applications such as integrator, differentiator, summing amplifier and others. An example of a widely used general-purpose op-amp is the 741/351. On the other hand, special purpose op-amps are used only for the specific applications they are designed for. For example the LM 380 op-amp can be used only for audio power applications;

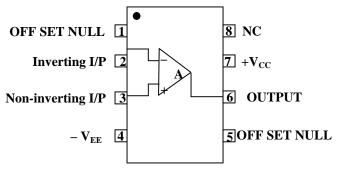

The pin configuration of most widely used 741 op-amp is given below

It is the most commonly used general-purpose op-amp. It has an integrated 30pF MOS capacitor. It has high input impedance (>  $M\Omega$ ), low output impedance (750  $\Omega$ ) and large voltage gain (200,000). From here onwards all the discussions are confined to  $\mu$ A741 op-amp.

The electrical parameters of op-amp are defined in the following paragraphs.

Fig (1.9) pin configuration of µA-741 op-amp

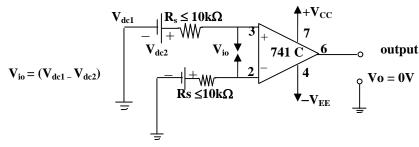

**Input offset voltage:** Input offset voltage is the voltage that must be applied between the two input terminals of an op-amp to null the output as shown in fig (1.10). In fig (1.10)  $V_{dc1}$  and  $V_{dc2}$  are dc voltages and  $R_s$  represents the source resistance. We denote input offset voltage by  $V_{i0}$ . This voltage  $V_{i0}$  could be positive or negative;

Fig (1.10) Defining input offset voltage V<sub>i0</sub>

For 741C, the maximum value of  $V_{i0}$  is 6 mV DC. The smaller the value of  $v_{i0}$ , the better the input terminals are matched.

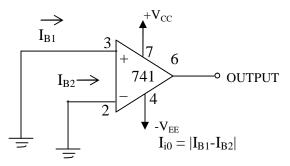

#### **Input offset Current:**

The algebraic difference between the currents into the inverting and non-inverting terminals is referred to as input offset current  $I_{i0}$  (see fig.1.11). In the form of an equation.

$$I_{i0} = \left|I_{B1}\text{-}I_{B2}\right|$$

Where  $I_{b1}$  is the current into the non-inverting input  $I_{b2}$  is the current into the inverting input

The input offset current for the 741C is 200 nA maximum. As the matching between the two input terminals is improved, the difference between  $I_{B1}$  and  $I_{B2}$  becomes smaller; that is, the  $I_{i0}$  value decreases further.

Fig (1.11) defining input offset current  $I_{i0}$

#### **Input Bias current:**

Input bias current  $I_B$  is the average of the currents that flow into the inverting and noninverting input terminals of the op-amp. In equation form

$$I_{B} = \frac{I_{B1} + I_{B2}}{2}$$

$I_B = 500$  nA maximum for the 741C, where as  $I_B$  for the precision 741C is  $\pm$  7 nA

Acharya Nagarjuna University

13

Note: that the input currents  $I_{B1}$  and  $I_{B2}$  are actually the base currents of the first differential amplifier stage.

#### **Differential input resistance:**

Differential i/p resistance  $R_i$  (often referred to as i/p resistance) is the equivalent resistance that can be measured at either the inverting or non-inverting i/p terminal with the other terminal grounded. For the 741C the i/p resistance is relatively high 2 M $\Omega$ .

**Input capacitance:** Input capacitance  $C_i$  is the equivalent capacitance that can be measured at either the inverting or non-inverting terminal with the other terminal grounded. A typical value of  $c_i$  is 1.4 pf for the 741C. This parameter is not listed in all op-amp-data sheets.

<u>Offset voltage adjustment ratio</u>: One of the features of the 741 family op-amps is an offset voltage null capability. The 741 op-amps pins 1 and 5 marked as offset null are for this purpose. As shown in figure 1.11 a 10kΩ potentiometer can be connected between offset null pins 1 and 5, and the wiper of the potentiometer can be connected to the negative supply  $-V_{EE}$ . By varying the potentiometer the output offset voltage can be reduced to zero volts. Thus the offset voltage adjustment range is the range through which the i/p offset voltage can be adjusted by varying the 10kΩ potentiometer. For the 741C is the offset voltage adjustment range is ±15mV. Very few op-amps have the offset voltage null capability. This means that for most op-amps , we have to design an offset voltage compensating net work in order to reduce the o/p offset voltage to zero.

<u>Common mode rejection ratio</u>: The common-mode rejection ratio (CMRR) is defined in several essentially equivalent ways by the various manufactures. Generally it can be defined as the ratio of the differential voltage gain  $A_d$  to the common mode voltage gain  $A_{cm}$ . That is

$$CMRR = \frac{A_d}{A_{cm}}$$

The differential voltage gain  $A_d$  is the same as the large signal voltage gain A, which is specified on the data sheets; The common mode voltage gain can be determined from the circuit.

$$\mathbf{A}_{\rm cm} = \frac{\mathbf{v}_{\rm ocm}}{\mathbf{v}_{\rm cm}} \,.$$

$v_{0cm} = o/p$  common mode voltage.

$v_{cm} = i/p$  common mode voltage.

$A_{cm} =$ common mode voltage gain.

Generally the  $A_{cm}$  is very small and  $A_d = A$  is very large; therefore the CMRR is very large, being a large value, CMRR is most often expressed is decibels (dB) for the 741C, CMRR is 90 dB typically.

<u>Slew rate (S.R)</u>: Slew rate is defined as the maximum rate of change of output voltage per unit of time and is expressed in volts per microseconds. In equation form

$$S.R = \frac{dv_o}{dt} / \text{maximum } V/\mu s$$

Slew rate indicates, how rapidly the output of an op-amp can change in response to changes in the input frequency with input amplitude constant. The slew rate changes with change in voltage gain and is normally specified at unity (+1) gain. The slew rate of an op-amp is fixed, therefore if the slope requirements of the o/p signal are greater than the slew rate, distortion occurs. The slew rate is one of the important factors in selecting the op-amp for an application, particularly at relatively high frequencies. One of the drawback of the 741C is its low slew rate (0.5 V/ $\mu$ s).

#### **Open-loop op-amp configurations:**

In the case of amplifiers, the term "open-loop" indicates that no connections, either direct or via another network exists between the o/p and i/p terminals. That is, the o/p signal is not fed-back in any form as part of the input signal and the "loop" that would have been formed with feedback is open.

When connected in open loop configuration the op-amp simply functions as a high gain amplifier. There are three open loop op-amp configurations:

- 1. The differential amplifier.

- 2. The inverting amplifier.

- **3.** The non-inverting amplifier.

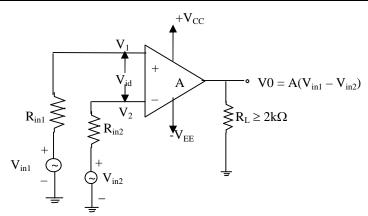

#### The differential amplifier:

Fig 1. 12 shows the open loop differential amplifier in which input signals  $v_{is1}$  and  $v_{is2}$  are applied to the positive and negative input terminals. Since the op-amp amplifies the difference between the two input signals, this configuration is called the differential amplifier.

15

Fig 1.12 Open loop differential amplifier

The op-amp is a versatile device because it amplifies both ac and dc input signals. This means that  $v_{is1}$  and  $v_{is2}$  could be either ac or dc voltages. The source resistance  $R_{in1}$  and  $R_{in2}$  are normally negligible compared to the input resistance  $R_i$ . Therefore, the voltage drops across the resistors can be assumed to be zero, which then implies that  $v_1 = v_{is1}$ , and  $v_2 = v_{is2}$ . Substituting these values of  $v_1$  and  $v_2$  in equation for output voltage, we get  $v_0 = A(v_{in1}-v_{in2})$

Thus, as expected the output voltage is equal to voltage gain A times the difference between the two input voltages. Also notice that the polarity of the output voltage is dependent on the polarity of the input difference voltage  $(v_{in1}-v_{in2})$ . In open loop configurations gain A is commonly referred to as open loop gain.

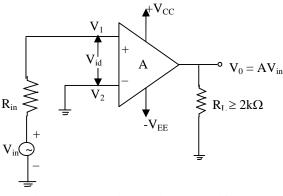

#### The inverting amplifier:

In the inverting amplifier only one input is applied and that, to the inverting input terminal.

The non-inverting input terminal is grounded. Since  $v_1=0$  and  $v_2=v_{\rm in}.$   $v_0=\ -Av_{\rm in}$

Fig 1.13 Inverting amplifier

The negative sign indicates that the output voltage is out of phase with respect to input by  $180^{\circ}$

or is of opposite polarity. Thus in the inverting amplifier the input signal is amplified by gain A and is also inverted at the output.

#### The non-inverting amplifier:

Fig 1.14 shows the open loop configurations of non inverting amplifier in this configuration the input is applied to the non inverting input terminal and the inverting input terminal is grounded.

In the circuit shown below  $v_1=v_{in}$  and  $v_2=0v$ . Therefore according to equation  $v_0 = Av_{in}$ . This means that the output voltage is larger than the input voltage. By gain A and is in phase with input signal.

Fig 1.14 Non-inverting amplifier

In all the three open loop configurations any input signal that is only slightly greater than zero drives the output to saturation level. This results from the very high gain A of the op-amp. Thus when operated in open loop, the output of the op-amp is either at negative saturation or positive saturation or switches between positive and negative saturation levels. For this reason the open loop configurations are not used in linear applications.

#### **1.4 Summary of the Lesson:**

A differential amplifier consists of two symmetrical common emitter stages and is capable of amplifying the difference between two input signals. Differential amplifier is capable of amplifying ac as well as dc input signals because it employs direct coupling. For proper operation of the differential amplifier, a transistor array and matched components must be used. The differential amplifier can be biased by using emitter bias (a combination of  $R_E$  and  $V_{EE}$ ), a

Acharya Nagarjuna University

constant current bias. The constant current bias is more preferable in differential amplifiers because it maintains the infinite input impedance for all the desired values of emitter currents  $I_E$ .

An ideal op-amp has infinite voltage gain, input resistance, CMRR and slew rate together with zero output resistance and output offset voltage. The equivalent circuit of op-amp is useful in analyzing the basic operating principles of an op-amp and in observing the effects of feedback arrangements. The voltage transfer characteristic curve of an op-amp is the graph of output voltage versus the differential input voltage. Differential, inverting and non-inverting amplifiers are the three open loop op-amp configurations in which the output signal is not fed back in any form as part of the input signal. When operated in the open loop; generally the op-amp's output is either at positive or negative saturation or switches between positive and negative saturation levels. This action is undesirable in linear applications, hence the op-amp's are rarely used in open loop configuration for the linear applications.

#### **1.5 Key terminology:**

Configuration : design of the circuit by employing the various possible networks is called configuration.

Decibel (dB); 1/ tenth of a Bell; Bell is unit of power ratio

Milli volts (mV); 1/1000 of a volts

Nano Ampere (nA);  $1nA = 10^{-9}$  ampere

Pico Farad (pF);  $1pF = 10^{-12}$  Farad

Saturation; when input voltage in the circuit exceeds a certain value, the output goes to the maximum value is called saturation

Pot (Potentiometer); variable wire wound resistor

#### **1.6 Self-assessment questions:**

- **1.** Explain the working of differential amplifier with a diagram.

- 2. What are common mode and differential mode gain of a differential amplifier?

- **3.** Derive expressions for the common mode voltage gain and differential mode voltage gain of a transistor differential amplifier and show that the common mode rejection ratio increases with emitter resistance.

- 4. What is meant by constant current bias? Explain its use.

- 5. What are the important stages of a typical operational amplifier?

- 6. Mention the important electrical characteristics of an ideal op-amp.

- 7. How far IC 741 electrical characteristics are nearer to the ideal characteristic of op-amp.

- 8. Explain the terms input offset voltage, input offset current, input bias current.

- 9. Explain why op-amp is not used in open loop configuration for linear applications.

#### **1.7 Reference Books:**

- (1) Operational Amplifiers and Linear Integrated Circuit Technology by Ramakanth A. Gaykwad Prentice Hall Inc.,

- (2) Basic Electronics by DC Tayal, Himalaya Publish Co.,

- (3) Semi Conductor Electronics by A K. Sharma New Age International Publishers

- (4) Foundations of ElectronicsBy D. Chattopadhyay, PC Rakshit, B. Saha, M.N. PurkaitSecond Edition, Wiley Eastern Ltd.,

- (5) Integrated Electronics By Millman & Halkias (MH)

#### Name of the Author

Dr D.Krishna Rao, M.Sc., M.Phil., Ph.D., Associate Professor, Physics Department, Nagarjuna University, Nagarjuna Nagar 522 510.

#### UNIT I LESSON 2

## **OPERATIONAL AMPLIFIERS -II**

1

#### **Objectives of the lesson:**

1. To discuss the effect of negative feed back on

- i) closed loop voltage gain

- ii) input resistance

- iii) output resistance and

- iv) band-width of op-amp.

- 2. To discuss the applications of op-amp

#### Structure of the lesson:

- 2.1 Introduction

- 2.2 Effect of negative feed back on closed loop op-amp

- 2.3 Applications of op-amp

- 2.4 Summary of the Lesson

- 2.5 Key terminology

- 2.6 Self-assessment questions

- 2.7 Reference Books

#### 2.1 Introduction :

As the open loop gain of op-amp is very high, only very small signals (of the order of micro-volts or less) having very low frequency may be amplified accurately with out distortion. However, signals this small are very susceptible to noise. Besides being large the open loop gain of the op-amp is not constant. The voltage gain varies with changes in temperature and power supply as well as with mass production techniques. The variations in voltage gain are relatively large in open-loop op-amp, in particular, which makes the open-loop op-amp unsuitable for many linear applications. In most linear applications the output is proportional to the input and is of the same type.

Further the bandwidth (band of frequencies for which the gain remains constant) of most openloop op-amps is negligibly small - almost a zero. For this reason, the open-loop op-amp is

| OpampII |

|---------|

|         |

impractical in ac applications. For instance the open loop bandwidth of the 741C is approximately 5Hz. However, in almost all ac applications a bandwidth larger than 5 Hz is needed.

Because of the above stated reasons, the open loop op-amp is generally not used in linear applications. Never the less in certain applications the open-loop op-amp is purposely used as a nonlinear device; that is a square ware output is obtained by deliberately applying a relatively large input signal. Open-loop op-amp configurations are most suitable in such applications.

We will be able to select as well as control the gain of the op-amp, if we introduce a modification in the basic circuit. This modification involves the use of feedback, that is, an output signal is fed back to the input either directly or via another network. If the signal fed back is of opposite polarity or out of phase by 180<sup>°</sup> with respect to input signal, the feedback is called of negative feedback. An amplifier with negative feedback has a self - correcting ability against any change in output voltage caused by changes in environmental conditions. Negative feedback is also known as degenerative feedback because when used it degenerates (reduces) the output voltage amplitude and in turn reduces the output gain.

Suppose the signal fed back is in phase with the input signal, the feedback is called positive feedback. In positive feedback, the feed back signal aids the input signal. For this reason it is also known as regenerative feedback. Positive feedback is necessary in oscillator circuits.

Therefore negative fed back stabilizes the gain, increases the bandwidth and changes the input and output resistances, when used in amplifiers. The price paid for these improvements is reduced voltage gain. Other benefits of negative feedback include a decrease in harmonic distortion and reduction in effect of input offset voltage at the output. Negative feed back also reduces the effect of variation in temperature and supply voltages on the output of the op-amp.

#### 2.2 Effect of negative feed back on closed loop op-amp

Amplifier performance can be altered considerably by sampling the output signal and sending a part of it to a mixer circuit where the feedback signal mixes with the input. Depending upon the phase relation ship between the input and feedback signals the resultant input can be less than the source voltage or more than that. If the effective input is less than source voltage it is called negative feed back. In this lesson you will learn the effect of negative feed back on various op amp parameters.

| Acharya Nagarjuna University 3 | Center for Distance Education |

|--------------------------------|-------------------------------|

|--------------------------------|-------------------------------|

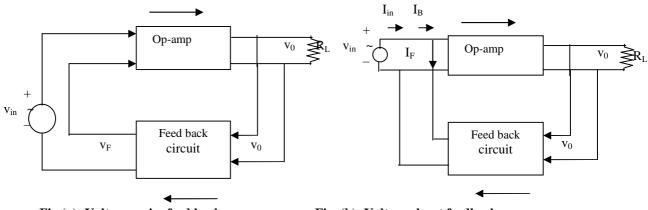

#### 2.2.1 Block diagram representation of feedback configurations:

An op-amp that uses the feedback is called a feedback amplifier. A feedback amplifier is sometimes referred to as a closed loop amplifier because the feedback forms a closed loop between the input and output. A feedback amplifier essentially consists of two parts: an op-amp and a feed back circuit. The feedback circuit can take any form what so ever, depending on the intended application of the amplifier. It means, the feedback circuit may be made up of either passive components, active components, or combinations of both. This chapter, in order to develop the basic feedback concepts presents only purely resistive feedback circuits.

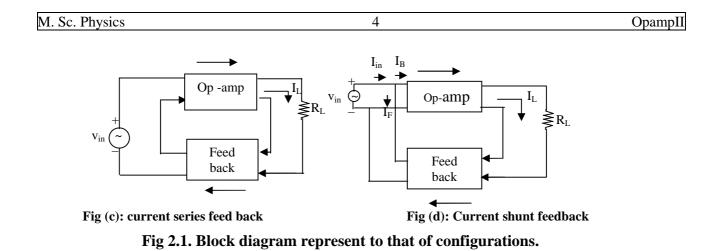

A closed loop amplifier can be represented by using two blocks, one for op-amp and another for a feedback circuit. There are four ways to connect these two blocks. These connections are classified according to whether the voltage or current is fed back to the input in series or parallel as follows:

- 1. Voltage- series feedback.

- 2. Voltage- shunt feedback

- 3. Current series feedback

- 4. Current shunt feedback

The four types of configurations are illustrated in fig (2.1). In fig (2.1)(a) and (b) the voltage across load resistor  $R_L$  is the input voltage to the feed back circuit. The feedback quantity (either voltage or current) is the output of the feedback circuit and is proportional to the output voltage. On the other hand in the current series and current shunt feedback circuits. [2.1 (c) and (d)] the load current  $i_L$  flows into the feedback circuit. The output of the feedback circuit is the feedback quantity which is proportional to the load current  $i_L$ .

Fig (b): Voltage shunt feedback

Note that in all four of these configurations, the signal direction through the op-amp is from the input to output. On the other hand, in the ideal case, the signal direction through the feedback circuit is exactly opposite, from output to input.

The voltage-series and voltage - shunt feedback configurations are important because they are most commonly used. In the present chapter the analysis of voltage series feedback is discussed, through computing voltage gain, input resistance, output resistance and bandwidth.

#### 2.2.2 Voltage series feedback amplifier:

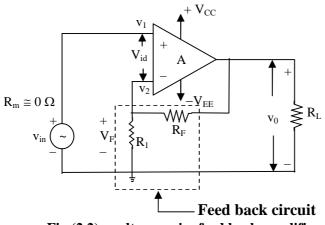

The schematic diagram of the voltage series feed back amplifier is shown in fig (2.2). The opamp is represented by its schematic symbol including the large signal voltage gain A, and the feedback circuit is composed of two resistances  $R_1$  and  $R_F$ .

Fig (2.2): voltage series feed back amplifier.

| Acharya Nagarjuna University 5 Center for Distance Edu |

|--------------------------------------------------------|

|--------------------------------------------------------|

The circuit shown in fig (2.2) is commonly known as a non- inverting amplifier with feedback (or closed loop non-inverting amplifier) because it uses feedback, and the input signal is applied to the non-inverting input terminal of the op-amp.

Before proceeding, it is necessary to define some important terms for the voltage series feed back amplifier of fig (2.2). Specially the voltage gain with and without feedback, and the gain of the feedback circuit are defined as follows.

Open loop voltage gain (or gain without feedback)  $A = \frac{V_o}{V_{id}}$ .

Closed –loop voltage gain (or gain with feedback)  $A_f = \frac{V_o}{V_{in}}$

Gain of the feedback current B=  $\frac{v_f}{v_o}$

#### 2.2.3 Negative feedback:

Returning to the circuit of fig (2) Kirchoff's voltage equation for the input loop is

$v_{id} = v_{in} - v_f$  -----(2.1)

Where  $v_{in} = input$  voltage

$V_f = feedback voltage$

V<sub>id</sub> =difference voltage

However, recall that an op-amp always amplifies the difference input voltage  $v_{id}$ . From eqn (2.1) the difference voltage is equal to input voltage  $v_{in}$  minus the feedback voltage  $v_f$ , in other words the feedback voltage opposes the input voltage (or is out of phase by  $180^0$  with respect to the input voltage). Hence the feedback is said to be negative. Returning to the analysis of voltage series feedback amplifier we should note that, it is performed by computing closed loop voltage gain, input resistance, output resistance, and the bandwidth.

#### 2.2.4 Closed loop voltage gain:

As defined previously, the closed loop voltage gain

$$A_{f} = \frac{V_{o}}{V_{in}},$$

However by equation  $v_0 = A (v_1-v_2)$ ,

Referring to fig (2.2) we see that

$v_1 = v_{in}$

$$v_2 = v_f = \frac{R_1 v_0}{R_1 + R_F}$$

since  $R_i >> R_1$

Therefore

$$v_0 = A \left( v_{in} - \frac{1}{R_1 + R_F} \right)$$

Rearranging the above equation, we get

$$v_{o} = \frac{A(R_{1} + R_{F})v_{in}}{R_{1} + R_{F} + AR_{1}}$$

Thus

$$A_F = \frac{v_o}{v_{in}} = \frac{A(R_1 + R_F)}{R_1 + R_F + AR_1}$$

(exact) ------ (2.2)

Generally, A is very large (typically 10<sup>5</sup>), therefore,

$AR_1 >> R_1 + R_F$  and  $R_1 + R_F + AR_1 \cong AR_1$

Thus

$$A_F = \frac{v_o}{v_{in}} = 1 + \frac{R_F}{R_1}$$

(ideal) ------ (2.3)

Equation (2.3) is important because, it shows that the gain of a voltage series feed back amplifier is determined by the ratio of the two resistors,  $R_1$  and  $R_F$ . For instance, if a gain of 11 is desired, we can then choose  $R_1 = 1k\Omega$  and  $R_F = 10k\Omega$  or  $R_1 = 100\Omega$  and  $R_F = 1k\Omega$ .

Another interesting result can be obtained from equation (2.3). As defined previously the gain or the feed back circuit (B) is the ratio of  $v_f$  to  $v_0$ . Referring to fig (2.2), the gain is

$$\mathbf{B} = \frac{\mathbf{v}_{\mathrm{f}}}{\mathbf{v}_{\mathrm{o}}}$$

$$B = \frac{R_1 v_0}{(R_1 + R_F) v_0} = \frac{R_1}{R_1 + R_F} \quad (2.4)$$

Comparing equations (2.3) and (2.4) we can conclude that

$$A_{\rm F} = \frac{1}{\rm B} \,(\text{ideal}) \,$$

------ (2.5)

This means that gain of the feed back circuit is the reciprocal of the closed loop voltage gain. In other words for given  $R_1$  and  $R_F$  the values of  $A_F$  and B are fixed. Besides that equation (2.5) is an alternative to equation (2.3)

Finally the closed loop voltage gain  $A_F$  can be expressed in terms or open loop gain A and feedback circuit gain B by rearranging equation (2.2) in the following manner we get

OpampII

$$A_{\rm F} = \frac{A \left( \frac{R_1 + R_{\rm F}}{R_1 + R_{\rm F}} \right)}{\frac{R_1 + R_{\rm F}}{R_1 + R_{\rm F}} + \frac{AR_1}{R_1 + R_{\rm F}}} \quad (2.6)$$

7

Using equation (2.4) yields

$$A_{\rm F} = \frac{A}{1 + AB} \quad \dots \quad (2.7)$$

Where  $A_F$  = closed loop gain

A = open loop gain

B = gain of the feed back circuit

AB = "loop gain"

#### **2.2.5 Input resistance with feedback:**

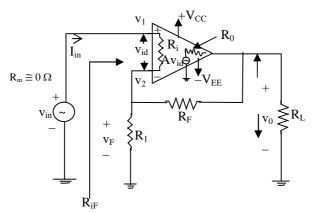

A voltage series feed back amplifier with the op-amp equivalent circuit is shown in fig (2.3). In this circuit  $R_i$  is the input resistance (open-loop) of the op-amp, and  $R_{iF}$  is the input resistance of the feed back amplifier. The input resistance with feedback is defined as

$$R_{if} = \frac{v_{in}}{i_{in}} = \frac{v_{in}}{v_{id} / R_{i}}$$

------ (2.8)

Fig 2.3 Derivation of input resistance with feedback.

However,

$$V_{id} = \frac{V_0}{A}$$

and  $v_0 = \frac{A}{1 + AB} v_{in}$  ------ (2.9)

$$R_{if} = R_{i} \cdot \frac{v_{in}}{v_0 / A}$$

------ (2.10)

$$R_{if} = AR_i \frac{V_{in}}{AV_{in}} = R_i (1+AB) - (2.11)$$

It means, the input resistance of the op-amp with feedback is (1+AB) times that without feedback.

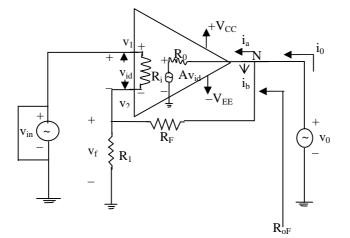

#### **2.2.6 Output resistance with feedback:**

Output resistance is the resistance determined looking back into the feedback amplifier from the output terminal, as shown in fig 2.4. This resistance can be obtained by using Thevenin's theorem for dependent sources. Specifically, to find output resistance with feed back  $R_{oF}$ , reduce the independent source  $v_{in}$  to zero, apply an external voltage  $v_0$  and then calculate the resulting current  $i_0$  in short, the  $R_{oF}$  is defined as follows:

$$\mathbf{R}_{\mathrm{oF}} = \frac{\mathbf{v}_{\mathrm{o}}}{\mathbf{i}_{\mathrm{o}}}.$$

Writing Kirchoff currents equation at the output node N, we get

$$i_{o} = i_{a} + i_{b}$$

.....(2.12)

Since  $R_F + R_1 \parallel R_i \implies R_0$ ,  $i_a \gg i_b$  therefore

$$i_0 \cong i_a$$

-----(13)

The current io can be found by writing Kirchoff's voltage equation for the output loop

$v_0 - R_0 i_0 - A v_{id} = 0$  ------ (2.14)

$$i_0 = \frac{v_0 - Av_{id}}{R_0}$$

$v_{id} = v_1 - v_2 = -v_f = -\frac{R_1 v_0}{R_1 + R_F} = -Bv_0$

therefore  $i_0 = \frac{V_0 + A.BV_0}{R_0}$

substituting the value of  $i_{\rm o}$  in equation, we get

$$R_{oF} = \frac{V_0}{(V_0 + ABV_0) / R_0} = \frac{R_0}{1 + AB} \quad (15)$$

This result shows that the output resistance of the voltage series feedback amplifier is 1/(1+AB) times the output resistance R<sub>o</sub> of the op-amp. That is, the output resistance of the op-amp with feedback is much smaller than the output resistance without feedback.

**Fig 2.4 Derivation of output resistance with feedback**

#### 2.2.7 Bandwidth with feed back:

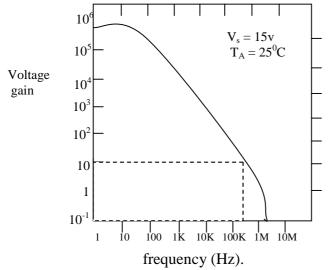

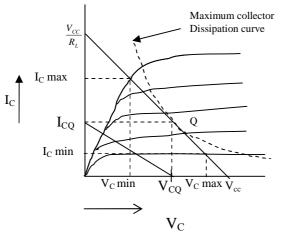

The bandwidth of an amplifier is defined as the band (range) of frequencies for which the gain remains constant. Manufacturers generally specify either the gain bandwidth product or supply open loop gain versus frequency curve for the op-amp. For the 741 op-amp the latter is typical.

The open loop gain versus frequency curve of the 741C op-amp is shown in Fig 2.5. From this curve for a gain of 200,000 the bandwidth is approximately 5Hz. In other extreme, the bandwidth is approximately 1MHz when the gain is unity. The frequency at which gain equals 1 is known as unity gain-band width. It is the maximum frequency the op-amps can be used for. Further more the gain bandwidth product obtained from the open loop gain versus frequency curve of fig 2.5 is equal to the unity gain bandwidth of an op-amp. However this holds true only for those op-amps like 741, which have just one break frequency below unity gain bandwidth.

Since the gain bandwidth product is constant, obviously the higher the gain the smaller the bandwidth and vice versa. As we have seen if negative feedback is used gain A decreases to A/1+AB. Therefore to obtain the closed loop bandwidth, the open loop bandwidth must be

9

10

multiplied by the same factor, by which the gain is divided, that is, by the factor (1+AB). In short.

Band width with feed back = (band width without feedback) (1+AB)

$$f_F = f_0 (1 + AB) - (16)$$

or alternatively,

$f_F$  = unity gain band width/closed loop gain = U.G.B.W /A<sub>F</sub> ------(17)

The closed loop bandwidth can also be determined from the open loop gain versus frequency plot. To do this we locate the closed loop voltage gain value on the gain axis and draw a parallel line through this value to the frequency axis. Then we project the point of inter section of the line with the curve on the frequency axis and read the value of the closed loop bandwidth. Using this procedure in figure 2.5. The bandwidth is approximately 100 KHz. for a closed loop gain of 10.

Fig 2.5 Open loop gain versus frequency curve of 741c.

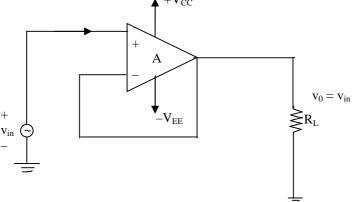

#### 2.2.8 Voltage follower:

The lowest gain that can be obtained from a non-inverting amplifier with feedback is 1. When the non-inverting amplifier is configured for unity gain, it is called a voltage follower

| Acharya Nagarjuna University | 11 | Center for Distance Education |

|------------------------------|----|-------------------------------|

|------------------------------|----|-------------------------------|

because the output voltage is equal to and in phase with the input. In other words, in the voltage follower, the output follows the input.

Although it is similar to the discrete emitter follower, the voltage follower is preferred because it has much higher input resistance, and the output amplitude is exactly equal to the input.  $\downarrow +V_{CC}$

Figure 2.6. Voltage follower.

To obtain the voltage follower from the non-inverting amplifier of figure (2.2), simply open  $R_1$  and short  $R_F$ . The resulting circuit is shown in figure 2.6. In this figure all the output voltage is feedback into the inverting terminal of the op-amp; consequently the gain of the feedback circuit is 1. (B =  $A_F$  = 1).

Since the voltage follower is a special case of the non-inverting amplifier all the formulae developed for the latter are indeed applicable to the former except that the gain of the feedback circuit is 1 (B=1) the applicable formulae are:-

$A_{F} = 1$   $R_{iF} = A R_{i}$   $R_{oF} = R_{o}/A$   $f_{F} = Af_{o}$   $vooT = \frac{\pm v_{sat}}{A}$ Since (1+A) \approx A

The voltage follower is also called a non-inverting buffer because when placed between two networks, it removes the loading on the first network.

| WI. Sc. I hysics 12 Opamp | M. Sc. Physics | 12 | OpampI |

|---------------------------|----------------|----|--------|

|---------------------------|----------------|----|--------|

#### **2.3 Applications of op-amp:**

Op-amps have many applications. Some are described below

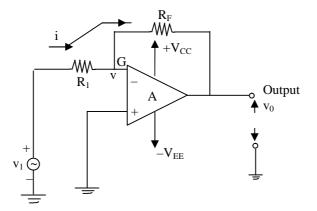

**2.3.1 Inverting amplifier:** The basic inverting amplifier with an input resistor  $R_1$  and feed back resistor  $R_F$  is shown in fig 2.7.

Fig 2.7 An inverting amplifier.

The non-inverting input terminal is grounded and the input voltage is  $v_1$  and the output voltage is  $v_0$ . Since the gain 'A' of the operational amplifier is very large, the voltage v at the inverting input terminal is very small. In fact, the voltage v is very close to the ground potential. That is, although the point G is not actually connected to the ground, it is held virtually at ground potential irrespective of magnitudes or the potentials  $v_1$  and  $v_0$ , the current i. is flowing through resistor  $R_1$  is given by  $i = \frac{v_1 - v}{R_1}$ . Assuming that the operational amplifier is ideal, having an infinite input impedance the current i will flow through  $R_F$  and not into the op-amp. Applying the Kirchoff's current law at the point G. We can have

Since the point 'G' is virtually ground i.e.  $v \approx 0$

From eqn.2.18. we get  $\frac{\mathbf{v}_1}{\mathbf{R}_1} = \frac{-\mathbf{v}_0}{\mathbf{R}_F}$

Acharya Nagarjuna University

Center for Distance Education

Rearranging equation 2.18.

We have

$$\frac{V_0}{V_1} = -\frac{R_F}{R_1}$$

------ (2.19)

The ratio of the output voltage to the input voltage is the gain of the amplifier. Hence the voltage gain is the ratio of feedback resistor  $R_F$  to the input resistance  $R_1$ . The negative sign indicates that the output voltage is inverted w.r.t. the input voltage. The input resistance  $(R_{in})$  of the whole amplifier is given by the ratio of voltage  $v_1$  and the input current  $\frac{v_1 - v_1}{R_1}$  that is

$$R_{in} = \frac{V_1}{\frac{V_1 - V}{R_1}} \approx R_1$$

------ (2.20)

since  $v \approx 0$ , note that  $R_{in}$  refers to the whole of the amplifier not to the op-amp which has an infinite input resistance

#### 2.3.2 Scale changer:

If use ratio  $\frac{R_F}{R_1}$  is denoted by k, a real constant, we get  $v_0 = -kv_1$ . That is, input voltage has been multiplied by the factor '- k' to give the output voltage scale. The circuit shown in fig 2.7 acts as scale changer. For such applications precision resistors are used to get accurate values for the scale factor 'k'

#### 2.3.3 Phase shifter:

If the resistance  $R_F$  and  $R_1$  in the circuit are replaced respectively by impedances  $z_F$  an  $z_1$  which are equal in magnitude but differ in phase angle, we can write

Since  $|z_F| = |z_1|$  and  $e^{j\Pi} = -1$ , the angles  $\phi_F$  and  $\phi_I$  represent respectively, phase angles of the independents  $z_F$  and  $z_I$ . The circuit is capable of shifting the phase of a sinusoidal input signal

13

| M. Sc. Physics 14 | OpampII |

|-------------------|---------|

|-------------------|---------|

voltage with out changing its magnitude. The amount of phase shift can be any thing between 0 and  $360^{\circ}$ .

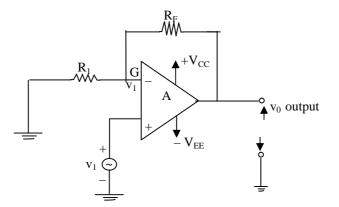

#### 2.3.4 Non- inverting amplifier:

The circuit diagram of non-inverting amplifier is shown in figure 2.8.

Fig 2.8 Circuit of non-inverting amplifier.

In this case the input voltage  $v_1$  is applied to the non-inverting input terminal. The potential of the point G is also  $v_1$ , since the op-amp gain is infinite. Then, as mentioned before, since the input current to the op-amp is negligible, we can write using Kirchoff's current law at the point G.

$$\frac{v_0 - v_1}{R_F} = \frac{v_1}{R_1} \quad \dots \quad (2.22)$$

Therefore, the gain of the amplifier is

$$\frac{v_0}{v_1} = 1 + \frac{R_F}{R_1} \quad \dots \quad (2.23)$$

Since the gain of the op-amp is 1 plus the ratio of the two resistors  $R_F$  and  $R_1$ . And also note that the output voltage is in phase with the input voltage.

#### 2.3.5 Summing amplifier:

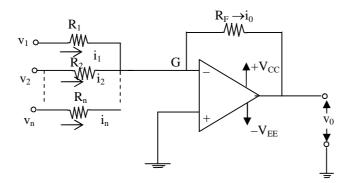

An adder or summing amplifier using op-amp is shown fig2.7. Here the point G is a virtual ground. Since the current flowing into the ground is equal to that flowing out of it we can write

Fig 2.9 an adder or summing amplifier

$$i_1 + i_2 + \dots + i_n = i_0 -\dots + (2.24)$$

$\frac{v_1}{R_1} + \frac{v_2}{R_2} + \dots + \frac{v_n}{R_n} = -\frac{v_0}{R_F} -\dots + (2.25)$

Solving equation. (2.25) for  $v_0$ , we get

$$v_0 = -R_F \left[ \frac{v_1}{R_1} + \frac{v_2}{R_2} + \dots + \frac{v_n}{R_n} \right]$$

------ (2.26)

If

$$R_1 = R_2 \dots = R_n = R$$

, we obtain  $v_0 = -\frac{R_F}{R} [v_1 + v_2 + \dots + v_n]$  ------(2.27)

Again if  $R_F = R$  we get

$v_0 = -[v_1 + v_2 + \dots + v_n]$  ------(2.28)

Equation 2.28 shows that the output voltage  $v_0$  is numerically equal to the negative sum of all input voltages  $v_1$  through  $v_n$ . Hence it was named as adder or summing amplifier.

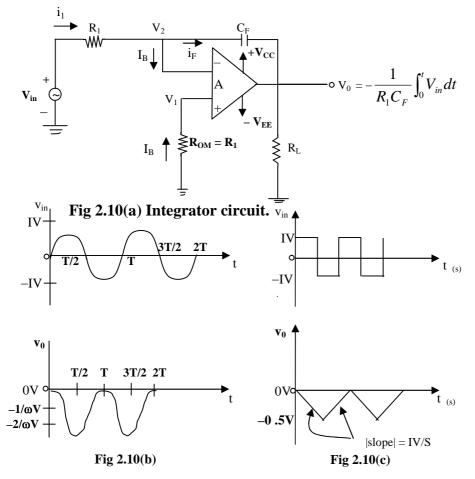

#### 2.3.6 Integrator:

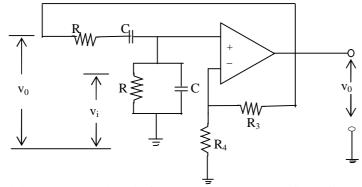

A circuit in which the output voltage waveform is the integral of the input waveform is the integrator or the integration amplifier. Such a circuit obtained by using a basic inverting amplifier configuration, if the feedback resistor  $R_F$  is replaced by a capacitor  $C_F$  and the relevant circuit is shown fig 2.10.

Fig 2.10 (b, c) input and ideal output waveforms using sine wave and square wave respectively  $R_1 C_F = 1$  second and  $v_{oo} = 0V$  assumed.

The expression for the output voltage  $v_0$  can be obtained by writing Kirchoff 's current equation at node  $v_2$ :

15

#### $i_1 = I_B \!+\! i_F$

Since  $I_B$  is negligibly small,  $\ i_1=i_F$

Recall that the relationship between current through and voltage across the capacitor

$$i_c = C \cdot \frac{dv_c}{dt}$$

Therefore

$$\frac{\mathbf{v}_{in} - \mathbf{v}_2}{\mathbf{R}_1} = \mathbf{C}_F\left(\frac{\mathbf{d}}{\mathbf{d}t}\right)(\mathbf{v}_2 - \mathbf{v}_0)$$

However,  $v_1 = v_2 \cong 0$  because A is very large. Therefore

$$\frac{\mathbf{v}_{\rm in}}{\mathbf{R}_1} = \mathbf{C}_{\rm F} \frac{\mathrm{d}}{\mathrm{d}t} \quad (-\mathbf{v}_0)$$

The out put voltage can be obtained by integrating both sides w. r. t. time

$$\int_{0}^{t} \frac{\mathbf{v}_{in}}{\mathbf{R}_{1}} \cdot dt = \int_{0}^{t} C_{F} \frac{d}{dt} (-\mathbf{v}_{0}) \cdot dt = C_{F} (-\mathbf{v}_{0}) + \mathbf{v}_{0} |_{t=0}$$

There fore

$$v_0 = -\frac{1}{R_1 C_F} \int v_{in} dt$$

-----(2.29)

Equation 2.29 says that the output voltage is directly proportional to the negative integral of the input and inversely proportional to the time constant  $R_1C_F$ . For example if the input is a sine wave, the output will be a cosine wave of if input is a square wave, the output will be a triangular wave as shown as fig 2.10 (b) and (c) respectively. Note that the wave forms are drawn on the assumption that  $R_1C_F = 1$  second and  $v_{00} = 0v$ .

For accurate integration of the input waveform, the time period of the input signal T must be longer than or equal to  $R_1C_F$ . Again, the  $R_{om}$  is used to minimize the effect or input bias current and the output offset voltage. The input offset voltage  $v_{i0}$  and the part of the input current charging the capacitor produce the error voltage at the output of the integrator. Therefore in the practical integrator shown in fig 2.10(a), a resistor  $R_F$  is connected across the feed back capacitor  $C_F$  to produce DC stabilization. In other words  $R_F$  limits the low frequency gain and hence minimizes the variations is the output voltage. Generally,  $R_F \cong 10R_1$ . The integrator is most commonly used in analog computers and analog to digital converters (ADC) and signal wave shaping circuits.

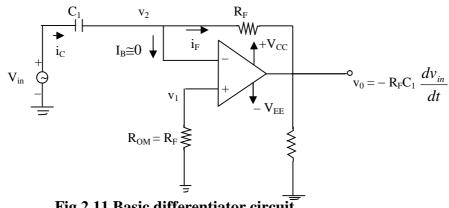

#### 2.3.7 The differentiator:

Fig 2.11 shows a differentiator or differentiating amplifier. As the name implies, the circuit performs the mathematical operation of differentiation: that is the output waveform is the derivative of the input waveform. The differentiator may be constructed form a basic inverting amplifier of an input resistor  $R_1$  is replaced by a capacitor  $C_1$

The expression for the output voltage can be obtained from Kirchoff's current equation written at node  $v_2$  as follows:

$$\begin{split} i_c &= I_B {+} i_F \\ \text{since } I_B &\cong 0, \end{split}$$

OpampII

$$\begin{aligned} I_{c} &= I_{F} \\ C_{1} \frac{d(v_{in} - v_{2})}{dt} &= \frac{v_{2} - v_{0}}{R_{F}} \end{aligned}$$

But  $v_1 = v_2 \cong 0v$ , because A is very large, therefore

$$C_1 \frac{dv_{in}}{dt} = -\frac{v_0}{R_F}$$

$$v_0 = -R_F C_1 \frac{dv_{in}}{dt}$$

------ (2.30)

Thus the output  $v_0$  is equal to the  $R_FC_1$  times the negative instantaneous rate of change of the input voltage  $v_{in}$  with time. Since the differentiator performs the reverse operation of the integrators function a cosine wave input will produce a sine wave output or triangular input will produce a square wave output. However, the differentiator of fig 2.11 will not do this because it has some practical problems. The gain of the circuit ( $R_F | Xc_1$ ) increases with increase in frequency at a rate of 20 dB/decade. This makes the circuit unstable. Also, the input impedance  $Xc_1$  decreases with increase in the frequency, which makes the circuit very susceptible to high frequency noise. When amplified, the noise can completely over ride the differentiated output signal.

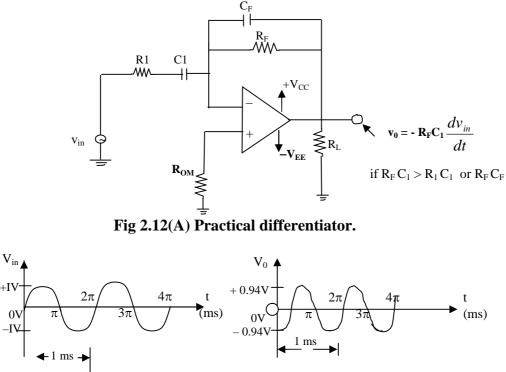

Both the stability and the high frequency noise problems can be corrected by an addition of two components;  $R_1$  and  $C_F$  as shown in fig 2.11 this circuit is a practical differentiator (fig 2.12)

Fig 2.12(B) sine wave input and resulting cosine wave output.

# 2.4 Summary of the Lesson:

Open loop op amp configuration is unsuitable for linear applications because of its very high voltage gain as well as its variation with temperature, power supply etc.

Therefore, we can select, as well as, control the gain of the op-amp, if we introduce a modification in the basic circuit This modification involves the use of fed-back, that is, the output signal is fed back to the input either directly or via another network. If the signal feed-back is  $180^{\circ}$  out of phase w.r.t. the input signal. Such a type of feedback is called negative feed back. Negative feedback is also known as degenerative feedback, because when used, it reduces the output voltage and in turn reduces the voltage gain and stabilizes the gain.

On the other hand if the signal fed-back is in phase with the input signal such type of feedback is called positive feed back. Positive feedback is also known as regenerative feedback, because the feedback signals aid the input signal. Positive feedback is needed in the oscillator circuits.

| M. Sc. Physics 20 | OpampII |

|-------------------|---------|

|-------------------|---------|

There are four types of closed loop configurations using negative feedback: voltage series, voltage shunt, current series and current shunt. Further these configurations are labeled according to whether the voltage or current is fed-back to the input in series or in parallel. The voltage series negative feedback configuration is generally known as non inverting amplifier if the feedback and the ideal closed loop voltage gain of the configuration depends only on the feedback network (components) and is independent of the internal or open loop gain A of the op-amp.

Introduction of the negative feedback in non-inverting amplifier increases the input impedance and bandwidth and decreases the output resistance; total output- offset voltage and the effect of varying environmental conditions on the gain. The voltage follower is the special case of noninverting amplifier.

Summing, scaling amplifiers can be constructed by using inverting, non-inverting and differential configurations. The integrator and differentiator are most widely used in signal wave shaping applications. Besides the integrator is used in analog computers and the differentiator is used as a rate of change detector in FM modulators.

# 2.5 Key terminology:

- 1. Active components: Active components can generate voltage or current or power Example: Battery, signal generator.

- 2. Passive components: The components only dissipate power Example: Resistor, capacitor.

- 3. Degenerative feedback: The output voltage is fed back to the input such that this voltage is  $180^{\circ}$  out of phase w.r.t. the source voltage. As a result, the effective input voltage decreases (degenerates) and this is called degenerative feedback or negative feedback.

#### 2.6 Self-assessment questions:

- 2.1 Mention two reasons why an open loop op-amp is unsuitable for linear applications.

- 2.2 What do you mean by feedback? List two types of feedback. Which type is used in linear applications?

- 2.3 Describe the four negative feedback configurations. Which configuration is most widely used?

- 2.4 Explain briefly why negative feedback is desirable in amplifier applications.

| Acharya Nagarjuna Universit | y 21 | Center for Distance Education |

|-----------------------------|------|-------------------------------|

|                             |      |                               |

- 2.5 How does negative feedback affect the close loop voltage gain, input resistance, output resistance and band width of voltage series feedback amplifier (closed loop non-inverting amplifier)

- 2.6 In what way is the voltage follower a special case of the non-inverting amplifier?

- 2.7 Explain the inverting and non-inverting amplifiers?

- 2.8 Explain the difference between the integrator and differentiator and give one application of each.

# 2.7 Reference Books:

- (1) Operational Amplifiers and Linear Integrated Circuit Technology by Ramakanth A. Gaykwad Prentice Hall Inc.,

- (2) Basic Electronics by DC Tayal, Himalaya Publish Co.,

- (3) Semi Conductor Electronics by A K. Sharma New Age International Publishers

- (4) Foundations of Electronics

By D. Chattopadhyay, PC Rakshit, B. Saha, M.N. Purkait Second Edition, Wiley Eastern Ltd.,

# Name of the Author

Dr D.Krishna Rao, M.Sc., M.Phil., Ph.D., Associate Professor, Physics Department, Nagarjuna University, Nagarjuna Nagar 522 510.

# UNIT I LESSON 3

# **OP-AMP CIRCUITS**

1

## **Types of Oscillators-Generators and 555 Timer**

#### **Objectives:-**

To explain

- i) The oscillator principle and discuss the various types of oscillators

- ii) The construction of square wave and triangular wave generators

- iii) The operation of the 555 Timer as an astable multi-vibrator.

#### Structure of the lesson

- 3.1 Oscillator principle

- 3.2 Working of R-C phase shift oscillator

- 3.3 Wien bridge oscillator

- 3.4 Square wave and triangular wave generators

- 3.5 The 555 timer

- 3.6 Summary of the Lesson

- 3.7 Key terminology

- 3.8 Self-assessment questions

- 3.9 Reference Books

Basically the function of an oscillator is to generate alternating current or voltage waveforms. More precisely, an oscillator is a circuit that generates a repetitive waveform of fixed amplitude and frequency with out any external input signal. Oscillators are used in radio, television, computers, and communications. Although there are different types of oscillators all of them work on the same basic principle.

Oscillators are classified into two basic categories: sinusoidal and non-sinusoidal. If the waveform generated looks like a sine or cosine wave, the circuit is called a sinusoidal oscillator and these circuits producing all other waveforms are called non-sinusoidal oscillators. Some times, the oscillators are also classified on the basis of frequency of the generated waveform, viz., audio frequency, radio frequency and ultra high frequency oscillators.

#### 3.1 Oscillator principle:

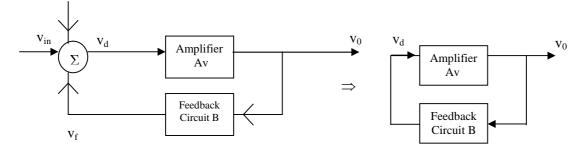

An Oscillator, as such, is a type of feedback amplifier in which part of the output is feed back to the input via a feedback circuit. If the signal feedback is of proper magnitude and phase, the circuit produces alternating currents or voltages. To visualize the requirement of an oscillator, consider the block diagram of figure 3.1.

However, here the input voltage is zero ( $v_{in} = 0$ ). Besides that, the feedback is positive because most oscillators use positive feedback. Finally, the closed loop gain of the amplifier is denoted by  $A_v$  rather that  $A_{F.}$

2

In figure 3.1

$$v_d = v_f + v_{in}$$

------ (3.1)

$v_0 = A_v v_d$  ------ (3.2)

$v_f = B v_0$  ------ (3.3)

Using these relation ships, the following equations are obtained

$$\frac{v_0}{v_{in}} = \frac{A_v v_d}{v_d - v_f} = \frac{A_v}{1 - (\mathbf{v}f / vd)} \quad ----- (3.4)$$

From equations (3.2) & (3.3), we have

$$\frac{\mathbf{v}_f}{\mathbf{v}_d} = \mathbf{A}_{\mathbf{v}} \mathbf{B} \quad \dots \quad (3.5)$$

Substitute equation (3.5) is equation (3.4), we have

$$\frac{v_0}{v_{in}} = \frac{A_v}{1 - A_v B} \quad ----- \quad (3.6)$$

However,  $v_{in} = 0$ , and  $v_0 \neq 0$  implies that

$A_V B = 1$

Expressed in polar form

$A_v B = 1$  and  $\phi = 0$  or  $360^0$  ------ (3.7)

Equation (3.7) gives the two requirements for oscillators:

- (1) The magnitude of the loop gain  $A_v B$  must be at least 1, and

- (2) The total phase of the loop gain  $A_v B$  must be equal to  $0^0$  or  $360^0$ . For instance, as indicated in fig (3.1), if the amplifier causes a phase shift of  $180^0$

| Acharya Nagarjuna University         | 3 | Center for Distance Education |

|--------------------------------------|---|-------------------------------|

| r tentar ya i tagar jana e intersity | 5 | Conter for Distance Education |

The feedback circuit must provide an additional phase shift of  $180^{\circ}$ , so that, the total phase shift around the loop is  $360^{\circ}$ . The waveforms shown in fig 3.1 are sinusoidal and are used to illustrate the circuit's action. The type of waveform generated by an oscillator depends on the components in the circuit and hence, may be sinusoidal, square or triangular. In addition, the frequency of the oscillation is determined by the components in the feedback circuit.

### 3.1.1 Oscillator types:

Because of their wide spread use, many different types of oscillators are available. These oscillators are summarized as follows.

| Types of Oscillator   | Frequency of Oscillation | Types of waveform generated |

|-----------------------|--------------------------|-----------------------------|

| 1. RC Oscillator      | 1. Audio frequency (AF)  | 1. Sinusoidal               |

| 2. LC Oscillator      | 2. Radio frequency (RF)  | 2. Square wave              |

| 3. Crystal Oscillator |                          | 3. Triangular wave          |

|                       |                          | 4. Saw-tooth wave           |

# **3.1.2 Frequency Stability:**

The ability of the oscillator circuit to produce waves at one exact frequency is called frequency stability. Although there may be a number of factors that cause changes in oscillator frequency, the primary factors are temperature changes and changes in the dc power supply. Temperature and power supply changes cause variations in the op-amp's gain, in junction capacitances and resistances of the transistors in an op-amp, as well as in an external circuit components. In most cases these variations can be kept small by careful design, using regulated power supplies, and by temperature control.

Another important factor that determine frequency stability, is the figure of merit Q of the circuit. The higher the Q, the greater the stability. For this reason crystals oscillators are far more stable than RC and LC oscillators, especially at higher frequencies. LC circuit and crystal are generally used for the generation of high frequency signals, while RC components are most suitable for audio frequency applications.

# 3.2 Working of R-C Phase Shift Oscillator:

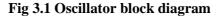

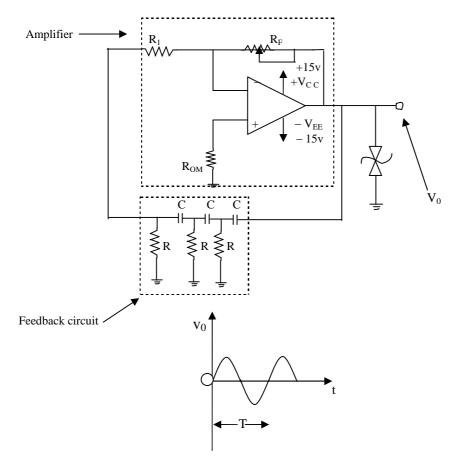

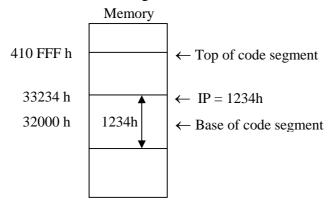

Fig 3.2 shows a phase shift oscillator, which consists of an op-amp, as amplifying stage and three RC cascaded networks in the feedback circuit. The feedback circuit provides feedback voltage from the output back to the input of the amplifier. The op-amp is used in the inverting mode; therefore any signal that appears at the inverting terminal is shifted by  $180^{\circ}$  at the output. An additional  $180^{\circ}$  phase shift required for oscillation is provided by the cascaded RC net works. Thus the total phase shift around the loop is  $360^{\circ}$  (or  $0^{\circ}$ ).

Fig (3.2) Phase shift oscillator and its output waveform

At some specific frequency when the phase shift of the cascaded RC networks is exactly  $180^{\circ}$  and the gain of the amplifier is sufficiently large, the circuit will oscillate at that frequency. This frequency is called the frequency of oscillation  $f_0$  and is given by

4

$$f_0 = \frac{1}{2\pi\sqrt{6}RC} = \frac{0.065}{RC}$$

------ (3.8)

At this frequency, the gain  $A_v$  must be at least 29. That is

$$\frac{R_{F}}{R_{1}} = 29$$

$$R_{F} = 29 R_{1} - \dots - (3.9)$$

Then the circuit will produce a sinusoidal waveform of frequency  $f_{0,}$  if the gain is 29 and the total phase shift around the circuit is exactly 360<sup>0</sup>. For a desired frequency of oscillator, choose a capacitor C<sub>1</sub> and then calculate the value of R from equation (3.8). A desired output amplitude, however, can be obtained with back-to-back Zeners connected at the output terminal.

4

# Analysis:-

5

Fig (3.3) RC network of the phase shift oscillator

Nodal equations are transformed into the s domain Writing Kirchoff's current law (KCL) at node  $v_1(s)$ , we get  $I_1(s) = I_2(s) + I_3(s)$

Writing KCL at node  $v_2$  (s)

$I_3(s) = I_4(s) + I_5(s)$

$$\frac{\mathbf{v}_1(s) - \mathbf{v}_2(s)}{1/SC} = \frac{\mathbf{v}_2(s)}{\mathbf{R}} + \frac{\mathbf{v}_2(s) - \mathbf{v}_3(s)}{1/SC}$$

$$v_1(s) [-SC] + v_2(s) \left[ \frac{1}{R} + 2SC \right] + v_3(s) [-SC] = 0$$

------ (3.11)

Writing KCL at node v<sub>3</sub>(s)

$I_5(s) = I_6(s)$

$$\frac{\mathbf{v}_2(\mathbf{s}) - \mathbf{v}_3(\mathbf{s})}{1/SC} = \frac{\mathbf{v}_3(\mathbf{s})}{\mathbf{R}}$$

6

$$v_{2}(s) [SC] + v_{3}(s) \left[ -\frac{1}{R} - SC \right] = 0$$

------ (3.12)

$v_{2}(s) = v_{3}(s) \left[ \frac{1}{RSC} + 1 \right]$

Substituting this in equation (3.11)

$$v_{1}(s)[-SC] + v_{3}(s) \left[ 1 + \frac{1}{SRC} \right] \left[ \frac{1}{RSC} + 2 \right] + v_{3}(s).(-SC) = 0$$

$$v_{1}(s) = v_{3}(s) \left[ -1 + \left( 1 + \frac{1}{RSC} \right) \left( 2 + \frac{1}{RSC} \right) \right]$$

Substituting this in equation (3.10)

$$v_{3}(s) \left[ -1 + \left(1 + \frac{1}{RSC}\right) \left(2 + \frac{1}{RSC}\right) \right] \left[ \frac{1}{R} + 2SC \right] + v_{3}(s) \left[ \frac{1}{RSC} + 1 \right] (-SC) = v_{0}(s)(SC)$$

$$v_{3}(s) \left\{ -1 + \left(1 + \frac{1}{RSC}\right) \left(2 + \frac{1}{RSC}\right) \left(\frac{1}{R} + 2SC \right) \right\} + v_{3}(s) \left((-SC) - \frac{1}{R}\right) = v_{0}(s)(SC)$$

$$v_{3}(s) \left[ -\frac{1}{R} - 2sC + \left[ \frac{1}{RSC} + 1 \right] \left[ 2 + \frac{1}{RSC} \right] \left[ \frac{1}{R} + 2SC \right] - SC - \frac{1}{R} \right] = v_{0}(s)(SC)$$

$$\sqrt{3}(s) \left( -3sC - \frac{2}{R} \right) + \left( \frac{RSC + 1}{RSC} \right) \left( \frac{2RSC + 1}{RSC} \right) \left( \frac{1 + 2RSC}{R} \right) = v_{0}(s)(SC)$$

$$v_{3}(s) \left[ \frac{\left( -3R^{3}S^{3}C^{3} - 2R^{2}S^{2}C^{2} \right) + \left( 1 + RSC \right) \left( 1 + 4R^{2}S^{2}C^{2} + 4RSC \right)}{R^{3}S^{2}C^{2}} \right] = v_{0}(s)(SC)$$

$$v_{3}(s) \left[ \frac{\left( -3R^{3}S^{3}C^{3} - 2R^{2}S^{2}C^{2} \right) + \left( 1 + RSC \right) \left( 1 + 4R^{2}S^{2}C^{2} + 4RSC \right)}{R^{3}S^{2}C^{2}} \right] = v_{0}(s)(SC)$$

$$v_{3}(s) \left[ \frac{N^{3}S^{3}C^{3} + 6R^{2}S^{2}C^{2} + 5RSC + 1 \right] = v_{0}(s) \left[ R^{3}S^{3}C^{3} \right]$$

$$\frac{v_{3}(s)}{v_{0}(s)} = \frac{S^{3}R^{3}C^{3} + 6S^{2}R^{2}C^{2} + 5SRC + 1}{S^{3}C^{2}} - (3.12 (a))$$

| Achary  | va Nag | garjuna | Unive | rsitv |

|---------|--------|---------|-------|-------|

| i ionai | ,      | Sarjana | 0     | ibity |

Next consider the op-amp part of the phase shift oscillator, the voltage gain of the op-amp

$$A_v = \frac{v_0(s)}{v_3(s)} = -\frac{R_F}{R_1}$$

------ (3.12 (b))

For an oscillator

$A_v B = +1.$  ------ (3.13)

Therefore, using equations 3.12(a) and 3.12(b), we have

Since it is an inverting amplifier  $A_v = -\frac{R_F}{R_1}$

$$\left(-\frac{R_{F}}{R_{1}}\right)\left[\frac{S^{3}R^{3}C^{3}}{S^{3}R^{3}C^{3}+6R^{2}S^{2}C^{2}+5SRC+1}\right] = 1$$

Substituting  $S = j\omega$ , and equating the real and imaginary parts, respectively, we get

$$\left(-\frac{R_{F}}{R_{I}}\right)\left[\frac{-j\omega^{3}R^{3}C^{3}}{-j\omega^{3}R^{3}C^{2}-6\omega^{2}R^{2}C^{2}+j5\omega RC+1}\right] = 1$$

$$\left(-\frac{R_{F}}{R_{I}}\right)(-j\omega^{3}R^{3}C^{3}) = -j\omega^{3}R^{3}C^{3}-6\omega^{2}R^{2}C^{2}+j5\omega RC+1 \quad \dots \quad 3.14$$

$$-6\omega^{2}R^{2}C^{2}+1=0 \text{ (Real)}$$

$$\omega^{2} = \frac{1}{6R^{2}C^{2}} \quad \dots \quad (3.14(a))$$

$$f = \frac{1}{2\pi\sqrt{6}RC} \quad \dots \quad (3.15)$$

$$\left(-\frac{R_{F}}{R_{I}}\right)(-\omega^{3}R^{3}C^{3}) = -\omega^{3}R^{3}C^{3}+5\omega RC \text{ (imaginary)}$$

7

M.Sc. Physics

**Op-Amp Circuits**

$$\frac{R_{F}}{R_{1}} = -1 + \frac{5}{\omega^{2} R^{2} C^{2}} \quad \dots \qquad (3.15 \text{ (a)})$$

8

From equation 3.14(a) and 3.15(a) we have

$$\frac{R_{F}}{R_{1}} = 29$$

----- (3.16)

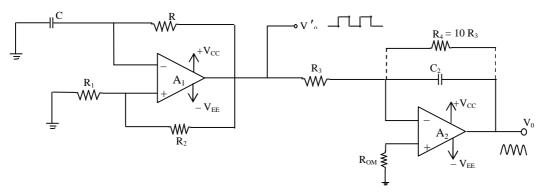

#### **<u>3.3 Wien Bridge oscillator:</u>**

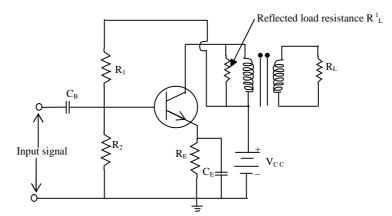

The circuit diagram for typical Wien bridge oscillator is shown in fig3.4. This involves an RC bridge circuit in which a frequency adjusting network is constructed of series combination of  $R_1$  and  $C_1$  connected from the output of the op-amp to the non-inverting input of the op-amp and of a parallel combination of  $R_2$  and  $C_2$  from the non-inverting input of the op-amp to the ground connections. The resistances  $R_3$  and  $R_4$  from the non-inverting input of the op-amp to the ground connections. The resistors  $R_3$  and  $R_4$  make the feedback path and determine the gain of the amplifier. The bridge circuit causes a phase shift of  $360^0$  between the output and input of the op-amp.

Fig 3.4(a) circuit configuration for Wien bridge oscillator

Fig 3.4(b) Redrawn circuit for  $R_1 = R_2 = R$ , and  $C_1 = C_2 = C$

# Acharya Nagarjuna University

Center for Distance Education

In the circuit of fig.4, the voltage  $v_{\rm i}$  across the parallel combination of R and C is fed back and is expressed as

9

$$v_i = \frac{v_0 Z_1}{Z_1 + Z_2}$$

----- (3.17)

Where

$$Z_1 = R ||C = \frac{R \frac{1}{j\omega C}}{R + \frac{1}{j\omega C}}$$

and  $Z_2$  (R in series with C) = R +  $\frac{1}{j\omega C}$  ------ (3.18)

$$v_{i} = \frac{v_{0} \left( \frac{R \frac{1}{j\omega C}}{R + \frac{1}{j\omega C}} \right)}{\left( \frac{R \frac{1}{j\omega C}}{R + \frac{1}{j\omega C}} \right) + \left( R + \frac{1}{j\omega C} \right)} \quad (3.19)$$

$$v_{i} = v_{0} \frac{R \frac{1}{j\omega C}}{R \frac{1}{jC} + R^{2} + 2R \cdot \frac{1}{j\omega C} - \frac{1}{\omega^{2}C^{2}}}$$

$$= v_{0} \frac{1}{1 + j\omega RC + 2 - \frac{j}{\omega RC}} = v_{0} \frac{1}{3 + j \left(\omega RC - \frac{1}{\omega RC}\right)} \quad ------ (3.20)$$

In order to have zero phase between  $v_{i}\,\text{and}\,v_{0},$  the j-terms must be zero i.e.,

$$\omega RC - \frac{1}{\omega RC} = 0;$$

$$\omega^2 = \frac{1}{R^2 C^2}$$

M.Sc. Physics

10

$$\omega = \frac{1}{\text{RC}}; \ \text{f} = \frac{1}{2\pi RC}$$

----- (3.21)

Substituting this frequency in equation (3.20)

$$v_i = \frac{1}{3} v_0$$

----- (3.22)

Equation 3.22 shows that there is a loss of voltage gain in the feedback network by a factor of 3. There fore, the amplifier should have minimum voltage gain as 3 for oscillations.

The input voltage  $v_1$  at the inverting point of the op-amp may be written as

$$v_i = \frac{v_0 R_4}{R_3 + R_4} \quad \dots \qquad (3.23)$$

Equaling equation (3.22) and (3.23), we get

$$\frac{1}{3} = \frac{R_4}{R_3 + R_4}$$

$$R_3 = 2R_4$$

----- (3.24)

Hence, for a stable operation of the oscillator:  $R_3$  is selected slightly larger than  $2R_4$  so that the maximum gain requirement is fulfilled.

# **<u>3.4 Square wave and Triangular wave generators</u> <u>3.4.1 Square Wave Generator:</u>**

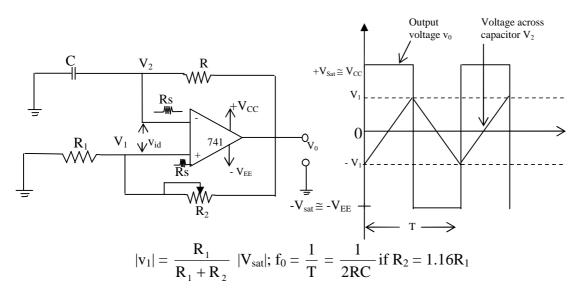

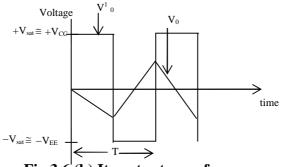

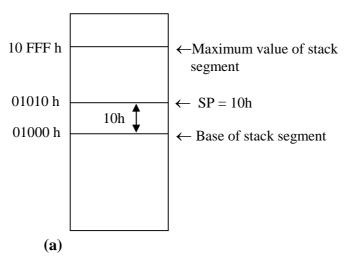

In contrast to sine wave oscillator, square wave outputs are generated when the op-amp is forced to operate in the saturated regions, that is, the output of the op-amp is forced to swing repetitively between positive saturation +  $V_{sat}$  ( $\cong$  +  $V_{CC}$ ) and negative saturation -  $V_{sat}$  ( $\cong$  -  $V_{EE}$ ), resulting in the square wave output. Such a circuit showed in fig(3.5). This square wave generator is also called a free-running multi-vibrator.

| Acharya Nagarjuna University | 11 | Center for Distance Education |

|------------------------------|----|-------------------------------|

|------------------------------|----|-------------------------------|

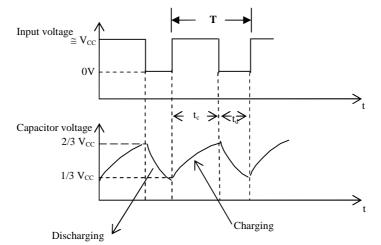

Assume that the voltage across the capacitor C is zero volts at the instant the dc supply voltages  $+V_{CC}$  and  $-V_{EE}$  are applied. This means that the voltage at the inverting terminal is zero initially. At the same instant, however, the voltage  $v_1$  at the non-inverting terminal is very small finite value, that is a function of the output offset voltage  $V_{ooT}$  and the values of  $R_1$  and  $R_2$  resistors. Thus the differential input voltage  $v_{id}$  is equal to the voltage  $v_1$  at the non-inverting terminal. Although very small, voltage  $v_1$  will start to drive the op-amp into saturation.

# Fig 3.5(a) Square wave generator (b) Wave form of output voltage. $v_0$ and capacitor voltage $v_2$ of the square wave generator.

For example, suppose that the output offset voltage  $v_{001}$  is positive and that, therefore voltage  $v_1$  is also positive. Since initially the capacitor C acts as a short circuit, the gain of the amplifier is very large (A); hence  $v_1$  drives the output of the op-amp to its positive saturation +  $V_{sat}$  with the output voltage of the op-amp as + $V_{sat}$ , the capacitor C<sub>2</sub> starts charging toward + $V_{sat}$  through the resistor, R. However, as soon as the voltage  $v_2$  across the capacitor is slightly more positive than  $v_1$ , the output of op-amp is forced to switch to a negative saturation, - $V_{sat}$ . With the op-amps output voltage as negative saturation, - $V_{sat}$  the

voltage v<sub>1</sub> across R<sub>1</sub> is also negative, since v<sub>1</sub> =

$$\frac{R_1}{R_1 + R_2}$$

(-V<sub>sat</sub>) ------ (3.25)