# SOLID STATE ELECTRONIC CIRCUITS AND DIGITAL ELECTRONICS

# B.Sc., Electronics III year - Paper - III

# Lesson writers

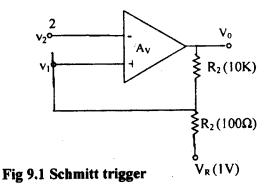

Prof. M. Rangacharyulu Professor in Physics (Retired)

Acharya Nagurjuna University

Nagarjuna Nagar - 522510

Dr.A.Radha Krishna Murthy

M.Sc., M.Phil, Ph.D.

Lecturer in Physics Chalapathi Institute of Engineering & Technology Chalapathi Nagar, LAM-522 034

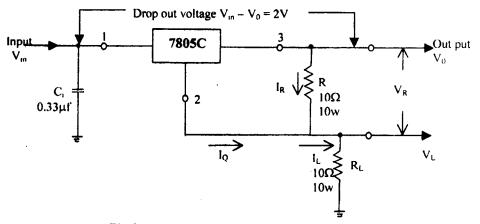

Dr.J.Sivarama Krishna, M.Sc., Ph.D. Assistant Professor in Physics L Acharya Nagarjuna University PG Centre S NUZVID, Krishna Dt.

Sri. V. Radha Krishna, M.Sc., M.Phil., Lecturer, Department of Physics SKBR Collge Amalapuram, E.G. District

Sri. S.V.Kumara Sastry, M.Sc., M.Phil Lecturer, Department of Physics SKBR Collge, Amalapuram - E.G. District

#### Associate Editor

Dr.A.Radha Krishna Murthy, M.Sc., M.Phil, Ph.D. Lecturer in Physics Chalapathi Institute of Engineering & Technology Chalapathi Nagar, LAM-522 034

#### Editor

Prof. M. Rangacharyulu, M.Sc., Ph.D. Professor in Physics (Retired) Acharya Nagarjuna University

Academic Coordinator Prof. S. Srechari Sastry, M.Sc., M.Phil, Ph.D. Professor in Physics Acharya Nagarjuna University

Director

#### Dr. Nagaraju Battu

MBA, MHRM, LLM, M.Sc. (Psy), MA(Soc.)., M.Ed., M.Phil., Ph.D. Dept. of HRM

# CENTRE FOR DISTANCE EDUCATION Acharya Nagarjuna University

Nagarjuna Nagar - 522510 Ph: 0863 - 2293299. (08645) 211023. 211024 Cell: 9848285518 e-mail: <u>anucde(ayahoo.com</u> Web site: www.nagarjunauniversity.ac.in

# B.sc., 3rd Year : Electronics, Paper - III

First Edition : 2009

New Impressions : 2021

No. of Copies : 318

# (C) Acharya Nagarjuna University

This book is exclusively prepared for the use of students of UG., Centre for Distance Education, Acharya Nagarjuna University and this book is meant for limited circulation only.

Published by : **Dr. Nagaraju Battu,** *Director,* Centre for Distance Education, Acharya Nagarjuna University

Printed at : **M/s Sri Sainadh Printers,** Vijayawada

#### FOREWORD

Since its establishment in 1976, Acharya Nagarjuna University has been forging ahead in the path of progress and dynamism, offering a variety of courses and research contributions. I am extremely happy that by gaining a B++ (80-85) grade from the NAAC in the year 2003, the Acharya Nagarjuna University is offering educational opportunities at the UG, PG levels apart from research degrees to students from over 285 affiliated colleges spread over the three districts of Guntur, Krishna and Prakasam.

The University has also started the Centre for Distance Education with the aim to bring higher education within reach of all. The centre will be a great help to those who cannot join in colleges, those who cannot afford the exorbitant fees as regular students, and even housewives desirous of pursuing higher studies. With the goal of brining education to the doorstep of all such people, Acharya Nagarjuna University has started offering B.A., and B.Com courses at the Degree level and M.A., M.Com., M.Sc., M.B.A., and L.L.M., courses at the PG level from the academic year 2003-2004 onwards.

To facilitate easier understanding by students studying through the distance mode, these self-instruction materials have been prepared by eminent and experienced teachers. The lessons have been drafted with great care and expertise in the stipulated time by these teachers. Constructive ideas and scholarly suggestions are welcome from students and teachers involved respectively. Such ideas will be incorporated for the greater efficacy of this distance mode of education. For clarification of doubts and feedback, weekly classes and contact classes will be arranged at the UG and PG levels respectively.

It is my aim that students getting higher education through the centre for Distance Education should improve their qualification, have better employment opportunities and in turn facilitate the country's progress. It is my fond desire that in the years to come, the Centre for Distance Education will go from strength to strength in the form of new courses and by catering to larger number of people. My congratulations to all the Directors, Academic Coordinators, Editors and Lesson-writers of the Centre who have helped in these endeavours.

> Prof. P. Rajasekhar Vice-Chancellor Acharya Nagarjuna University

# B.SC III YEAR ELECTRONICS PAPER – III SOLID STATE ELECTRONICS CIRCUITS AND DIGITAL ELECTRONICS

# UNIT I

Rectifier and Power Supplies: (a) Rectifier: Half wave, Full wave and Bridge Rectifiers and their efficiency Ripple factor, regulation, harmonic components in rectifier output. (b) Types of filters: Choke input filter (inductor), Shunt capacitor filter,

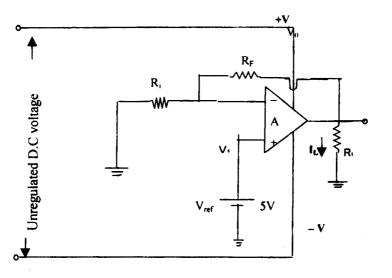

L - section and P section filters. (c)Regulated power supplies: Series regulated power supply.

**Power amplifier:** Expression for power, harmonic distortion and efficiency. Push-pull **amplifiers**, Class A, Class B and Class AB. Advantages and disadvantages

#### UNIT II

Operational Amplifier Basic (emitter controlled) difference amplifier and its parameters operational amplifier characteristics of 'n ideal Op Amp. Block diagram of an ideal Op Amp Feedback arrangement Open loop gain, common mode voltage gain, common mode rejection ratio (CMRR), slew rate, offset voltage and bias currents. Op Amp analysis: Concept of virtual ground . Analysis of inverting amplifier summing amplifier, current and voltage followers Application: Op Amp as comparator, voltage regulator, free running multivibrator and to solve a simple second order differential equation.

#### UNIT III

Modulation and detection (Qualitative) : Need for modulation. Amplitude modulation and detection : Analysis of amplitude modulated wave, side bands. Simple amplitude modulator circuit and its working. Detection of AM wave (diode detector). Frequency modulation and detection: Advantages of frequency modulation, side bands (frequency components) Working of a simple frequency modulator. Detection of FM waves.

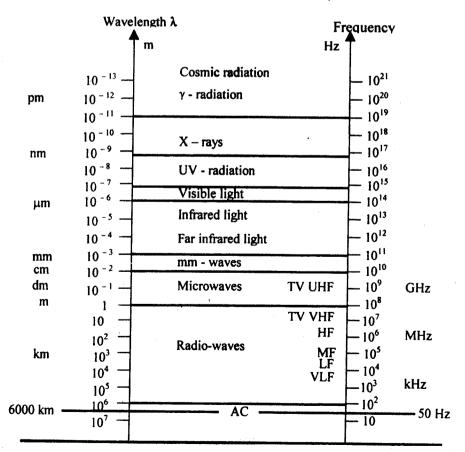

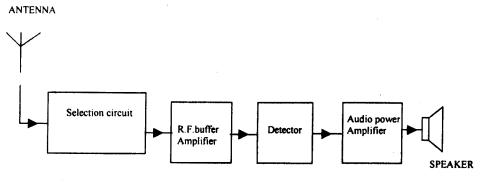

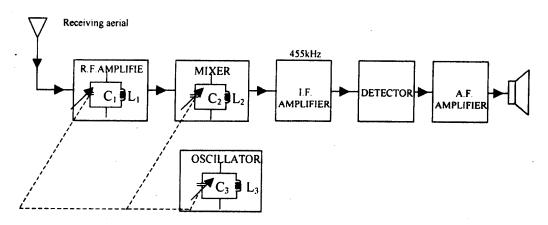

Electromagnetic spectrum: Identification of areas where radio waves and microwaves are applied. Radio broadcasting and reception, explanation of working of super hetrodyne receiver (block diagram). Microwaves, their properties and applications.

#### **UNIT IV**

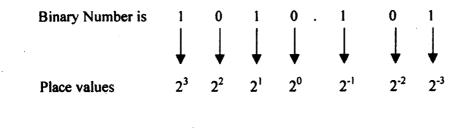

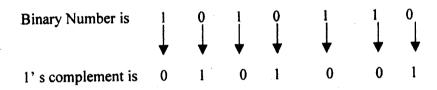

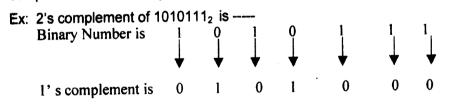

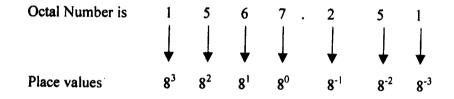

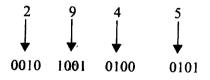

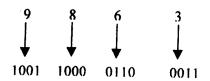

Digital Electronics: (a) Number system Binary number system, converting binary to decimal and vice versa, Binary addition and subtraction (1's and 2's compliment methods). hexadecimal number system. Converting binary to hexadecimal and vice versa, converting hexadecimal to decimal and vice versa. Binary coded decimal(8421) and gray code, conversion between binary and gray codes ,The ASCII code (American Standard Code for Information Interchange).

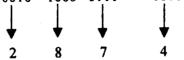

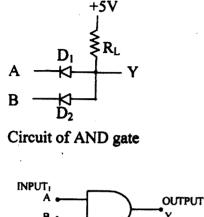

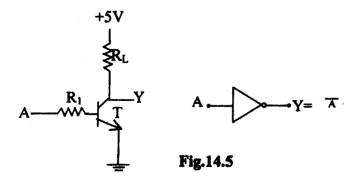

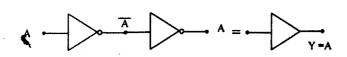

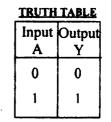

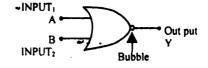

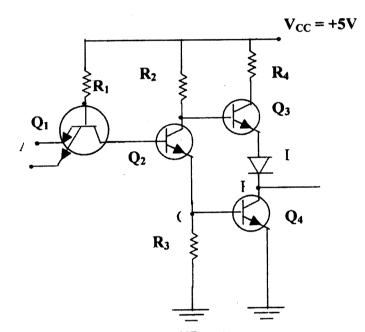

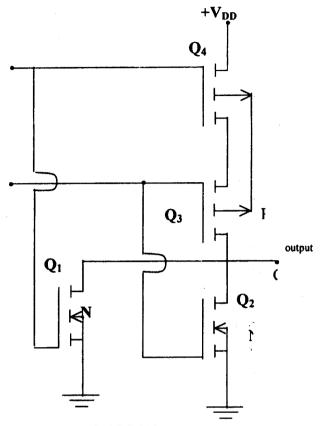

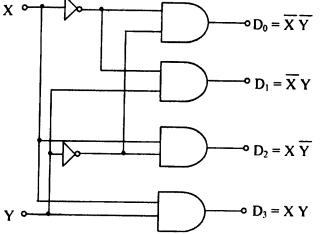

(b) Logic gates: OR, AND, NOT gates: Truth tables, realization of these gates using diodes, resistors and transistor circuits. Positive and negative logic. Laws of Boolean algebra, Universal building blocks NAND and NOR gates, transistor - transistor logic (TTL), complimentary metal oxide semiconductor (CMOS) logic.

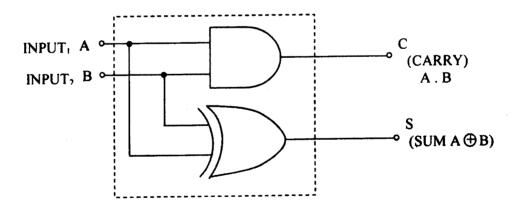

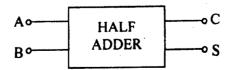

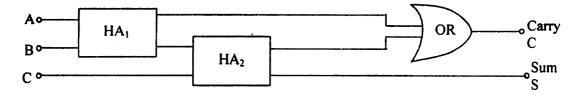

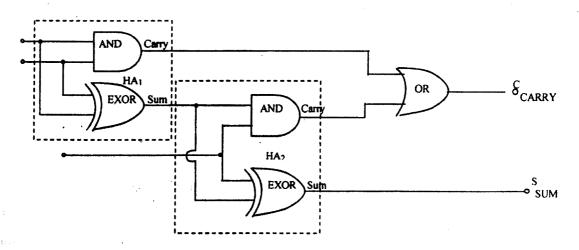

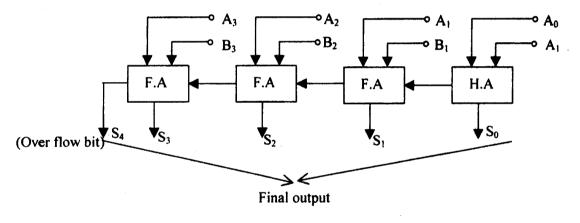

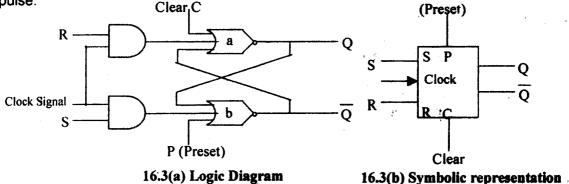

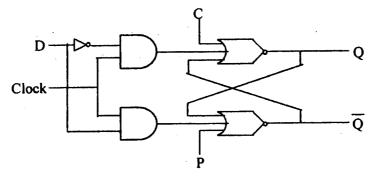

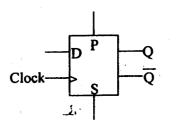

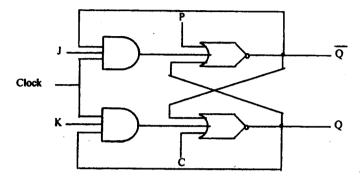

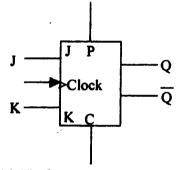

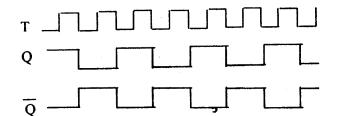

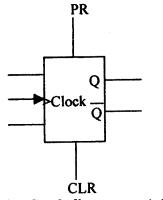

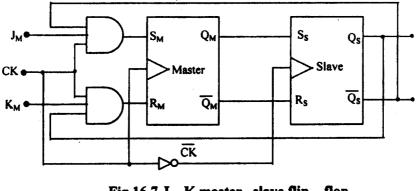

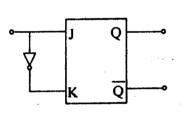

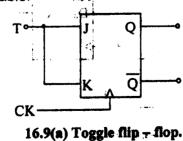

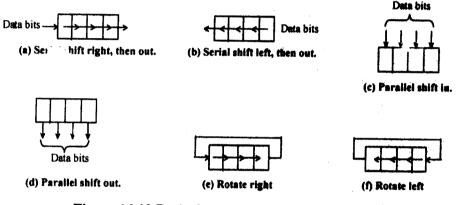

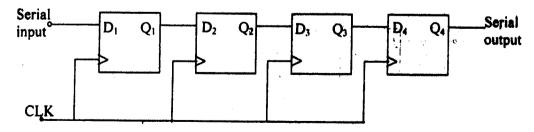

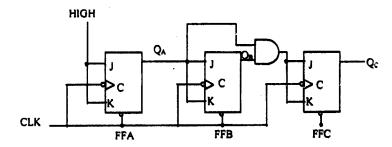

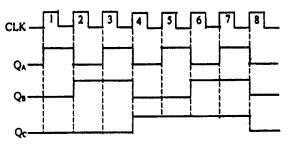

(c) Combinational logic circuits: Half, full and parallel adders, sequential logic circuits flip-flops (RS, T, D, JK and Master slave JK) their working and truth tables, Binary and decade counters and shift registers.

#### **TEXT BOOKS**

- 1. Integrated Electronics by Millman and Halkias

- 2. Electronic Communications by Kennedy

- 3. Principles of Digital Electronics by Malvino and Leach

- 4. Basic Electronics and Linear Circuits Bhargava etc

# **REFERENCE BOOKS**

- 1. A text lab manual in Electronics by ZBAR (Tata Mc graw Hill)

- 2. Electronics fundamentals by JD Ryder

- 3. Modern Electronics Communications by Gray and Miller

- 4. Digital Electronics by William H.Gothman

- 5. Op Amp and linear integrated Circuits by Ramakant Gayakwad

- 6. Electronic Devices and Circuits by Samuel Seely

# **B.SC III YEAR (ELECTRONICS)**

# (For the students admitted in 2004-05 & onwards )

# Practical Paper III

- 1. DC power supply and filters

- a) Full wave rectifier with various filters

- b) Transistor DC regulated power supply and finers

2a. Astable multivibrator (using OP AMP 741)

- 2b Astable Multivibrator using Transistors/opamps

- 3. Schmitt Trigger using OP AMP 741

- 4. Bistable Multivibrator using Transistors

- 5. Emitter follower

- 6. Verification of truth tables OR, AND, NOT, NAND, NOR, EX-OR gates and verification of De Morgan's theorems

- 6a) IC logic gates 6b) Logic gates with Discrete components

- 6c) De Morgan's Theorems

- 7. Construction of other gates using NAND and NOR gates & construction of halfadders and full adders, verifying their truth tables.

- 7a) Universal Logic gates

- 7b) Half-Adder & Full Adder

- 8. Testing and verifying Flip-Flops (RS,D and JK)

- 9. Testing and verifying counters Binary (7493), BCD (7490)

Division module N (1 to 9) & shift registers using JK flip-Flops.

- 10.OP Amp characteristics --off set null voltage, bias currents, CMRR and slew rate

- 11. OP amp 741 as

- (a) DC inverting Amplifier (b) Non-inverting Amplifier (DC and AC) © Summer

- (d) Differential Amplifier Tr

- 12. OP amp 741 as .

- a) Integrator b) Differentiator

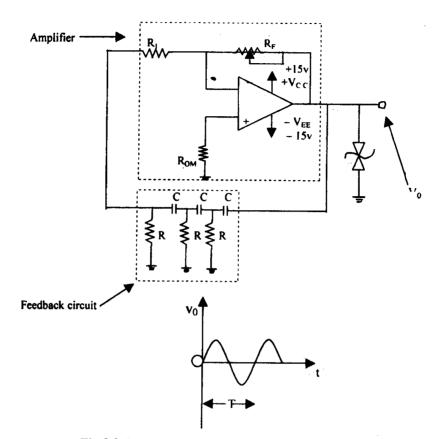

- 13. Op Amp Wein Bridge oscillator

- 14. Voltage regulator using IC 7805

- 15. Construction of Astable multivibrator using IC 555.

Any twelve experiments

# B.Sc. DEGREE EXAMINATION.

#### (Examination at the end of Third Year)

#### Part II - Electronics

# Paper III- SOLID STATE ELECTRONIC CIRCUITS AND DIGIGITAL ELECTRONICS Time: There hours Maximum: 100 marks

#### PART A - (4 x 14 =56marks)

#### Answer ALL questions.

# Each question carries 14 marks.

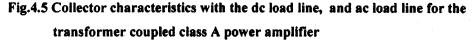

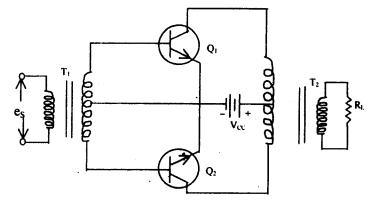

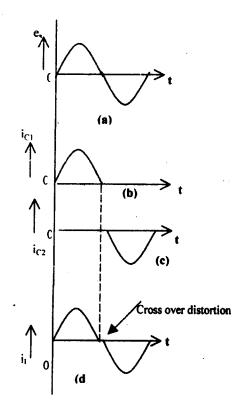

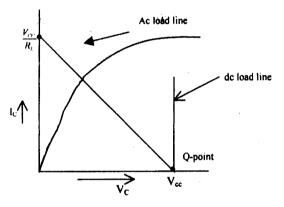

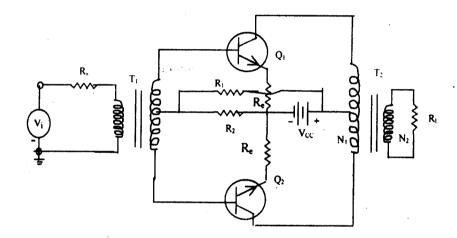

(a) Draw the circuit diagram of a Class – B Push – pull. Amplifier and Discuss its working. Derive expressions for collector efficiency and Output Power. Give the reasons for cross – over Distortion in Push – Pull Amplifiers.

Or

(b) Draw a neat circuit diagram of Bridge Rectifier and describe its operation. What are the advantages and disadvantages?

(a) What is an OP-AMP? Mention the characteristics of an ideal OP-AMP.

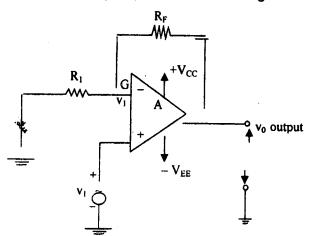

Explain the concept of Virtual – Ground in OP-AMP. Draw the circuit of an OP-AMP Inverting- Amplifier and explain its action.

Ör

(b) Draw the pin diagram of Timer IC 555. Draw the circuit of an Astable Multivibrator using OP-AMP and describe its working.

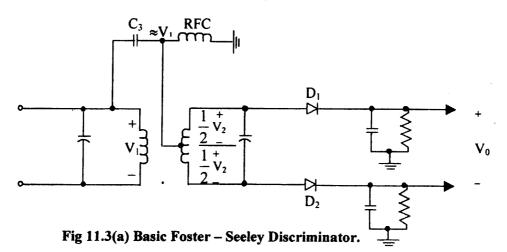

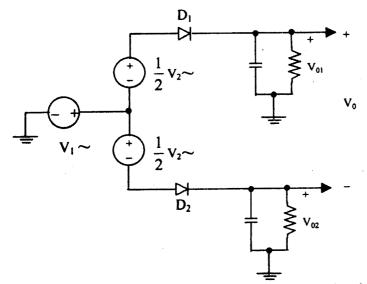

3. (a) Explain how the FM waves are detected. Describe the principle and working of a discriminator.

Or

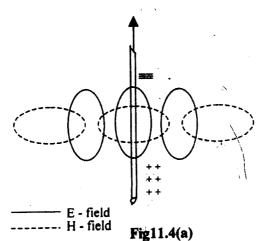

(b) What are important properties of Microwaves and Mention their applications in detail.

(a) What are sequential logic circuits? Describe the working of Master Slave JK Flip Flop.

Or

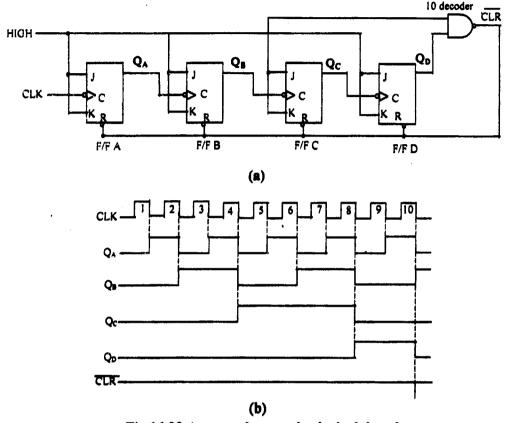

(b) Draw the block diagram of a Decade Counter and Explain its Operation. Sketch the timing diagram.

# PART B - $(4 \times 5 = 20 \text{ marks})$ Answer any FOUR questions.

- 5. What are the advantages of Bridge Rectifier and Full Wave Rectifier?

- 6. Explain Cross-Over distortion? Explain how it can be eliminated.

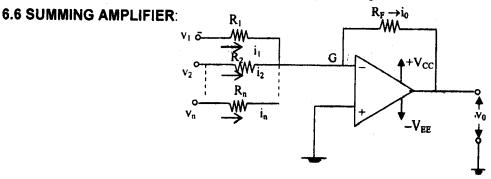

- 7. Explain the working of OP-AMP summing Amplifiers.

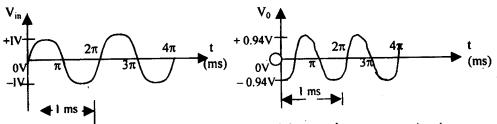

- 8. Draw the circuit diagram of a OP-AMP to solve a Second Order Differential equation.

- 9. Briefly explain how AM wave is detected.

- 10. Draw the full adder circuit, and explain its operation.

- 11. State and explain the basic laws of Boolean Algebra.

#### PART C - $(4 \times 6 = 24 \text{ marks})$

### Answer any FOUR questions.

- 12. Define the terms:

- (a) Ripple factor and

- (b) Regulation

7

- (c) Rectifier Efficiency as related to Full Wave Rectifier.

- 13. When a sinusoidal signal is fed to an Amplifier, the Output current is given by.

$i_{C} = 15\sin 400t + 1.5\sin 800t + 1.2\sin 1200t + 0.5\sin 1600t$ . Calculate

- (a) Second, Third and Fourth percentage Harmonic Distortions.

- (b) Percentage increase in power due to distortion.

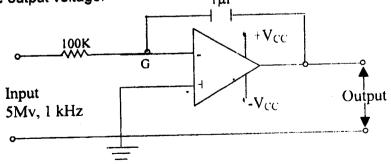

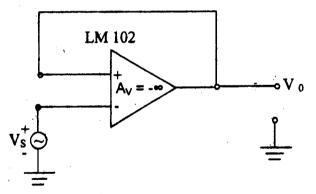

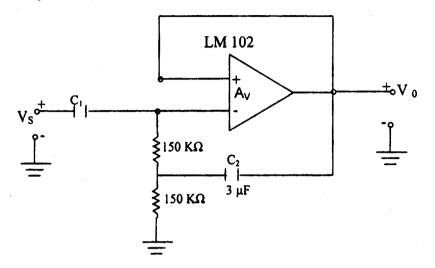

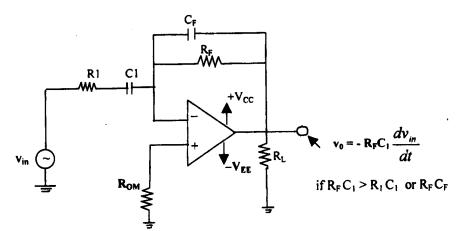

- 14. 5mV, 1 kHz sine wave is applied at the input of the OP-AMP as shown in fig. Find the output voltage.  $1\mu F$

15. Calculate the modulation index of an FM wave which has carrier swing of 160 kHz and has been modulated by a signal 10 kHz.

٦

16. Prove the following Boolean identity

$$ABC + A\overline{B}C + AB\overline{C} = A(B+C).$$

- 17. Multiply :

- (a) 1100 x 101

- (b) 1110 x 111

- 18. Explain the working of Super Heterodyne Receiver.

CONTENTS

PAGES

# B.Sc III YEAR ELECTRONICS PAPER - III Solid State Electronic Circuits and Digital Electronics

| CONTENTS                                                | FAGES             |

|---------------------------------------------------------|-------------------|

| UNITI                                                   |                   |

| Lesson 1: Half-wave and full - wave rectifiers          | 1.1–1.21          |

| Lesson 2: D.C. Power supply with various filters        | 2.1 <b>–2</b> .19 |

| Lesson 3: Regulated D.C. Power supplies                 | 3.1-3.15          |

| Lesson 4: Power Amplifiers                              | 4.1-4.20          |

| UNIT II                                                 |                   |

| Lesson 5: Operational Amplifiers – I                    | 5.1- 5.16         |

| Lesson 6: Operational Amplifiers - II                   | 6.1-6.14          |

| Lesson 7: Operational Amplifiers – III                  | 7.1-7.16          |

| Lesson 8: Operational Amplifiers – IV                   | 8 1- 8.22         |

| Lesson 9: Op Amp circuits and IC voltage regulators     | 9.1– 9.13         |

| UNIT III                                                |                   |

| Lesson 10: Amplitude modulation and detection           | 10.1–10.13        |

| Lesson 11: frequency modulation and detection           | 11.1–11.10        |

| Lesson 12: Radio broadcasting, reception and microwaves | 12.1–12.15        |

| UNIT IV                                                 |                   |

| Lesson 13: Number systems                               | 13.1–13.20        |

| Lesson 14: Digital electronics - basic logic gates      | 14.1–14.17        |

| Lesson 15: Combinational logic circuits                 | 15:1-15.13        |

| Lesson 16: Sequential logic circuits                    | 16.1–16.26        |

|                                                         |                   |

**Practical Manual**

à

#### **UNIT I**

# HALF-WAVE AND FULL - WAVE RECTIFIERS

#### **OBJECTIVES OF THE LESSON**

To know the working of half-wave and full-wave rectifiers

#### STRUCTURE OF THE LESSON

- 1.1 Introduction

- 1.2 Unregulated D.C. power supply using half wave rectifier

- 1.3 Half-wave rectifier

- 1.3.1 Average current and voltage components

- 1.3.2 Harmonic components of rectified output

- 1.3.3 Other important parameters

1.4 Full - wave rectifier

- 1.4.1. Using a center- tapped transformer

- 1.4.2. Average current and voltage components

- 1.4.3 Harmonic components of rectified output

- 1.4.4 Other parameters

1.5 Full-wave rectifier using diode bridge (Bridge rectifier)

1.5.1 Average current and voltage components of a full-wave bridge rectifier

- 1.5.2 Advantages and disadvantages of bridge rectifier

- 1.5.3 Peak loss

- 1.5.4 Comparison of half-wave and full-wave rectifier

1.6 Summary

1.7 Key Terminology

1.8. Self assessment Questions

1.9 Text and Reference Books

#### **1.1 INTRODUCTION**

Most of the electronic circuits need D.C. voltage supply. Even though we plug a computer or T.V. to A.C. mains, in side it, there will be a circuit which converts the Mains A.C voltage to D.C. voltage. This D.C. voltage is used to power the electronic circuit with transistors and 'Cs. So, it is very essential to know how to build a D.C voltage source from A.C mains supply. Alternately Batteries can be used to provide required D.C. voltage, but they are very

A

#### UNIT I

# HALF-WAVE AND FULL - WAVE RECTIFIERS

#### **OBJECTIVES OF THE LESSON**

To know the working of half-wave and full-wave rectifiers

#### STRUCTURE OF THE LESSON

- 1.1 Introduction

- 1.2 Unregulated D.C. power supply using half wave rectifier

- 1.3 Half-wave rectifier

- 1.3.1 Average current and voltage components

- 1.3.2 Harmonic components of rectified output

- 1.3.3 Other important parameters

1.4 Full - wave rectifier

- 1.4.1. Using a center- tapped transformer

- 1.4.2. Average current and voltage components

- 1.4.3 Harmonic components of rectified output

- 1.4.4 Other parameters

1.5 Full-wave rectifier using diode bridge (Bridge rectifier)

- 1.5.1 Average current and voltage components of a full-wave bridge rectifier

- 1.5.2 Advantages and disadvantages of bridge rectifier

- 1.5.3 Peak loss

- 1.5.4 Comparison of half-wave and full-wave rectifier

- 1.6 Summary

- 1.7 Key Terminology

- 1.8. Self assessment Questions

1.9 Text and Reference Books

#### **1.1 INTRODUCTION**

Most of the electronic circuits need D.C. voltage supply. Even though we plug a computer or T.V. to A.C. mains, in side it, there will be a circuit which converts the Mains A.C voltage to D.C. voltage. This D.C. voltage is used to power the electronic circuit with transistors and 'Cs. So, it is very essential to know how to build a D.C voltage source from A.C mains supply. Alternately Batteries can be used to provide required D.C. voltage, but they are very

expensive and need regular charging, maintenance and increase the weight and size of the gadget. In this lesson we learn how to assemble a D.C voltage source from A.C mains using rectifier circuits.

A. D.C. power supply provides a certain amount of constant current at a given constant D.C. voltage here, *constant* means, there will be no variation in their values with time. Transistor based circuits need a constant operating voltage in the range between 0 to  $\pm 30$ VD.C. Linear IC based circuits need about  $\pm 15$ V D.C.<sup>+</sup> Digital I.C based circuits need  $\pm 5$ V D.C. The current rating for the transistor and Linear I.C circuits and simple digital circuits is usually between 10 to 500mA D.C. For Microprocessor and other high power circuits it will be up to 5 Amps. So, we confine our discussion to Power circuits of this category.

To construct a D.C. power supply, we usually draw power from mains supply, which is provided **as** Single phase 220V A.C. with 5A A.C. current at a frequency of 50Hz. We can have a D.C. power supply constructed in three ways.

1. Simple unregulated power supply with filter circuit.

- 2. Transistor or IC based Regulated power supply

- 3. Switching Mode Power Supply

We consider the first two types in detail as per the syllabus.

#### 1.2 Unregulated D.C. Power supply

An unregulated power supply is one that simply converts the A.C. voltage taken from the A.C supply into required D.C. voltage supply at the required current. It consists of the following parts:

1. Step down transformer

- 2. Rectifier

- 3. Filter circuit

# 1.2.1 Transformer

A transformer consists of two sets of inductance coils wound on a common core. In a power transformer, the first coil called Primary coil or simply Primary is so designed to draw the needed power from A.C mains supply. The other coil even though wound on the same former, is electrically insulated from primary but is magnetically coupled. Whenever there is a change in primary current, a voltage is induced in the secondary coil.

Whatever is the current and voltage requirement, to construct a D.C.' power supply, we have to select a power transformer that takes A.C electrical power in its primary coil from electrical mains and provides the required A.C voltage in its secondary coil. A transformer enables us to step up or step down the A.C. voltage to the required level and also provides electrical isolation from A.C. mains. As you

Ĺ

studied in detail about transformers, coils, capacitors, chokes, in your 1<sup>st</sup> year course, that knowledge is assumed here.

Transformers that provide A.C output voltage less than that of primary voltage are called **Step-down** transformers. The secondary to primary voltage ratio depends upon the turns ratio of the transformer. A transformer designed to handle low power will be small in size when compared to a transformer that delivers larger current at the same voltage as it is provided with thicker wires and good quality core.

#### 1.2.2 Rectifier

A Rectifier is device that converts alternating current into unidirectional current. The process of converting A.C to D.C is called *Rectification*. A diode acts as a rectifier. The unidirectional conducting property of diode is used to remove either positive or negative half of the sinusoidal signal applied to it. Time average of a sine wave over a cycle is zero. By removing either the positive or negative half cycle from it, we can mathematically show that the output of a rectifier consists of certain amount of D.C voltage, and superposed on it, various sine waves, whose frequencies are multiples of the frequency of applied A.C voltage. This alternating A.C. component is called *Ripple*. Ripple component is filtered out using a filter circuit to obtain pure D.C.

For high voltage rectification vacuum tube diodes are preferred. For voltages needed in transistor and I.C circuits, semiconductor diodes are preferred. For low voltage high current applications, Selenium bridge rectifiers are used. A diode has two electrodes called **Anode** and **Cathode**. Current flows through the diode when anode is more positive than cathode. In a semiconductor p-n junction diode, the p-terminal is identical to anode and n-region is the equivalent of cathode.

#### 1.2.3 Filter circuit

Most rectifier circuits use a reservoir capacitor at the output terminal to smooth the rectified voltage in to D.C. voltage. It is important to note that the presence of the reservoir capacitor substantially changes the rectified voltage waveform and often affects the diode current and voltage requirements. A large capacitance whose reactance is negligible when compared to the  $R_L$  will serve the purpose. It has the further advantage that the capacitor stores the charge and retains the potential during the off-period of the diode, thereby improving the amplitude of D.C voltage.

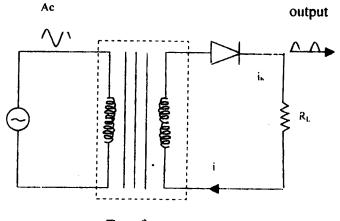

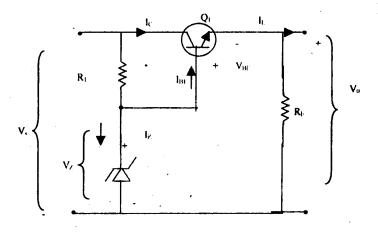

If we use a single rectifier to rectify A.C. it is called a *half-wave rectifier* as we are using only half of the sinusoidal input wave. See Fig 1.1

#### **1.3 HALF-WAVE RECTIFIER**

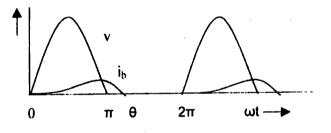

Fig.1.1 shows the circuit of a half-wave rectifier. The rectified output consists of half sinusoids as shown in the Fig.1.1. This has a time average of D.C and several A.C components which have to be filtered, to get pure D.C voltage across load resistance R<sub>L</sub>. A semiconductor diode with required current rating and reverse breakdown voltage is used for rectification. As these diodes are designed to handle larger power than ordinary diodes, these are usually called Power rectifiers. Usually a BY127 or 1N4001 serves the purpose for low power applications.

#### Working

A diode conducts only during positive half cycle of the input cycle when connected as shown in the Fig.1.1. So, current flows during positive half cycles of the input and produces a voltage drop across the load resistance  $R_L$ . The repetition frequency of the half sinusoids is same as the input A.C waveform. As it is, this rectifier is not suitable as D.C. source, as the output is a time varying waveform. However, it has a time averaged D.C component also. This D.C voltage is obtained by filtering out the A.C portion of the output using a suitable filter.

Transformer

When a dicde is forward biased, the voltage drop across it is  $V_{\text{F}}$  and the output voltage is

$$V_{po} = V_{pi} - V_{F}$$

Note that  $V_p = 1.414V_i$

Where V<sub>i</sub> is the rms level of the sinusoidal input voltage.

The diode peak forward current is

$$I_{\mu} = \frac{V_{\mu\nu}}{R_{\mu}}$$

Ç

During the negative half-cycle of the input, the reverse biased diode offers a very high resistance. So only a very small reverse current  $(I_R)$  flows giving an output voltage,

$$-V_o = -I_R \times R_L$$

While the diode is reverse biased, the peak voltage of the negative half-cycle of the input is applied across its terminals. Thus, the peak reverse voltage of peak inverse voltage (PIV), applied to the diode is

$$V_R = PIV = V_{pi}$$

#### 1.3.1 Average current and voltage components

For the sinusoidal input to the transformer, the output voltage across the secondary of transformer will also be sinusoidal having frequency same as that of the input. Let the voltage across the secondary of transformer be given as  $v = V_0 \sin \omega t$  where  $V_0$  is the peak voltage across the secondary and  $\omega_{2\pi}'$  is the frequency. If  $R_f$  be the dynamic forward resistance of the diode,  $R_s$  the resistance of the secondary of the transformer and  $R_L$  the load resistance the instantaneous current  $i_b$  through resistance  $R_L$  is given by

$= I_0 \sin \omega t$

Where the maximum value of current

$$I_0 = \frac{V_0}{R_f + R_S + R_L}$$

Since this current ib flows only for half cycle, hence

$i_b = I_0 \sin \omega t$  during  $0 \le \omega t \le \pi$ ,

and  $i_b = 0$  during  $\pi < \omega t \le 2\pi$ ,

.....(1.3.2)

Average values:

The average value of current (Iav) through RL can be given by

$$I_{av} = I_{dc} = \frac{\int_{0}^{T} i_{b} dt}{\int_{0}^{T} dt} = \frac{\int_{0}^{T} \sum_{0}^{\pi} I_{0} \sin \omega t \, dt + \int_{1}^{T} 0.dt}{\int_{0}^{T} dt}$$

$$= \frac{-\frac{I_0}{\omega} [\cos \omega t]_0^{V/2 = \pi/\omega} + 0}{2\pi/\omega} = \frac{I_0}{\pi}$$

=  $\frac{V_0}{\pi (R_f + R_s + R_L)}$  .....(1.3.3)

Hence the dc or average voltage at the load RL will be

This shows that the dc output voltage depends not only upon the load current but the diode and transformer resistance also.

These two equation give the dc or or average power across the load  $R_L$ .

$$\therefore P_{dc} = V_{dc} I_{dc} = I_{dc}^2 R_L = \frac{V_0^2 R_L}{\pi^2 (R_L + R_s + R_L)^2} \qquad (1.3.5)$$

#### R.M.S value of the current:

The Root Mean Square or effective value of current in the circuit can be given as

$$I_{rms}^{2} = \frac{\int_{0}^{T} i_{b}^{2} dt}{\int_{0}^{T} dt} = \frac{\int_{0}^{T} \frac{\pi}{\omega} I_{0}^{2} \sin^{2} \omega t dt + \int_{0}^{T} \frac{dt}{dt}}{\int_{0}^{T} \frac{\pi}{\omega} dt} = \frac{I_{0}^{2}}{4},$$

Or  $I_{rms} = \frac{I_{0}}{2} = \frac{V_{0}}{2(R_{f} + R_{s} + R_{f})}.....(1.3.6)$

Thus the I<sub>rms</sub> is greater than the dc component I<sub>dc</sub>. This also show that the R.M.S value of the half rectified current is not the same as the R.M.S value of the sinusoidal current which is  $I_0 / \sqrt{2}$ .

### 1.3.2 Harmonic components of rectified output

Frequency components of rectified output: The output current of the rectifier can be assumed as consisting of several harmonics of frequency and can be written in terms of Fourier series as

$$i_b = A_0 \sum A_n \cos n\omega t + \sum B_n \sin n\omega t,$$

ĺ

Where the coefficients A<sub>0</sub>, A<sub>n</sub> and B<sub>n</sub> are given by

$$A_0 = \frac{1}{T} \int i_h dt, A_n = \frac{2}{T} \int i_h \cos n\omega t \, dt$$

and  $B_n = \frac{2}{T} \int i_h \sin n\omega t dt.$

On solving the integrals using the limiting values of  $i_b$  from equation, we get equation as

$$i_{b} = I_{0} \left[ \frac{1}{\pi} + \frac{1}{2} \sin \omega t - \frac{2}{3\pi} \cos 2\omega t - \frac{2}{15\pi} \cos 4\omega t \dots (1.3.7) \right]$$

The first term of the series gives the directs or average component and is equal to the Eq.(1.3.7). The second term has its frequency same as that of the supply with peak value  $I_0/2$ . The rms value of this fundamental frequency component will be

$$= \frac{peak \ value}{\sqrt{2}} = \frac{\frac{I_0}{2}}{\sqrt{2}} = \frac{I_0}{2\sqrt{2}}.$$

(1.3.8)

The third term gives the second harmonic term. The other frequency terms are also there in the equation. So through the load resistance  $R_L$ , dc as Well as ac components will pass.

#### 1.3.3 Other important parameters of half-wave rectifier

**Rectifier efficiency:** The efficiency of the rectifier, also known as ratio of rectification, is defined as

$\eta$  = Direct output power / Alternating input power from transformer secondary

$$=\frac{P_{dc}}{P_{ac}}$$

The input power from transformer secondary is the power that would be indicated by a wattmeter placed in the rectifying circuit with its terminals connected across the transformer secondary. Thus

$$P_{ac} = I_{rmix}^{2} R_{f} + I_{rmix}^{2} R_{L} = \frac{1}{4} I_{0}^{2} (R_{f} + R_{L})$$

$$\therefore \eta = \frac{I_{0}^{2} R_{L}}{\pi^{2}} \times \frac{4}{I_{0}^{2} (R_{f} + R_{L})} = \frac{4R_{L}}{\pi^{2} (R_{f} + R_{L})}$$

or

$$P_{c} = \frac{4}{\pi^{2} (R_{f} + R_{L})} = \frac{40.6}{\pi^{2} (R_{f} + R_{L})}$$

% of  $\eta = \frac{4}{\pi^2 [1 + R_f / R_L]} \times 100 - \frac{40.0}{[1 + R_f / R_L]}$  .....(1.3.9)

The given the theoretical efficiency of a half wave rectifier which increase as  $R_f/R_L \rightarrow 0$ . Thus the maximum efficiency will be 40.6%. But the rectifier delivers maximum output power when the load resistance is equal to  $R_f$ . So, the efficiency is now reduced to 20.3 percent only.

Transformer Utilization Factor (TUF): The transformer utilization factor TUF is defined as

TUF = dc power delivered to the load /ac rating of the transformer secondary

$$=\frac{P_{dc}}{P_{ac}(rated)}.$$

The rating of the transformer secondary is different from the actual power delivered by the secondary. It is the product of the rated R.M.S. voltage of the secondary  $V_a / \sqrt{2}$  and the actual R.M.S. current flowing through the secondary  $I_0 / 2$ . Hence

$$TUF = \frac{(I_0 / \pi)^2 R_{I_0}}{(V_0 / \sqrt{2})(I_0 / 2)}.$$

sin ce  $V_0 = I_0 (R_f + R_s + R_b),$

#### Therefore

Thus the TUF is different from the rectifier efficiency.

**Ripple factor:** This represents the fluctuating, pulsating or alternating part in the output of rectifier. As obtained from Fourier analysis the output wave consists of altering components called as ripples. So ripple factor is a measure of the fluctuating or pulsating components i.e. purity of output. It is defined as the ratio of the effective value of the ac components of the current or voltage to the direct or average value of the current or voltage i.e.

Ripple factor(r) =  $\frac{effective value of ac components}{dc value of the components}$

The output current of a rectifier  $(I_{ma})$  consists of the direct component  $(I_{dc})$  and effective value of all ac components  $(I'_{ma})$ .

$$I_{rms}^{2} = I_{dc}^{2} + I_{rms}^{2} \text{ or } I_{rms}^{1} = (I_{rms}^{2} - I_{dc}^{2})^{1/2}$$

$$\therefore r = \frac{I_{rms}^{1}}{I_{dc}} = \left(\frac{I_{rms}^{2}}{I_{dc}^{2}} - 1\right)^{1/2}$$

ł

So for a half wave rectifier

Similarly  $V'_{rms} = 1.2 \, V_{dc}$ .

This shows that the effective values of the ac components of the output exceeds the dc value of the output. Thus we see that the half-wave rectifier is not a suitable device for obtaining dc.

**Peak Inverse Voltage:** Peak inverse voltage (PIV) is defined as the maximum voltage present across the diode ends when the diode is reverse biased and thus does not conduct. For half-wave rectifier the non-conducting periods is during the negative part of applied alternating wave and its peak valve is equal to  $V_0$ . Thus for a half-wave rectifier PIV =  $V_0$ . To avoid breakdown, PIV must be less than the PIV rating of the diode.

**Voltage regulation**: It is a measure of the ability of a rectifier to maintain a specified output voltage with the variation of load resistance and is defined as

Voltage regulation(V.R.) =

$$\frac{output at no load - output at full load}{output at full load}$$

In a perfect voltage regulator the output voltage does not charge with the load resistance. For a half-wave rectifier we have,

Assuming here  $(R_f+R_s) \le R_L$ , the higher powers of  $(R_f + R_s) / R_L$  are neglected for load (open circuit,  $R_i = \infty$ ),  $I_{dc} = 0$  and  $V_{dc} = V_0 / \Pi$ .

At full load, we have

$$(V_{dc})_{\text{tull load}} = (V_{dc})_{\text{norload}} - (I_{dc})_{\text{full load}} \cdot (R_f + R_S)$$

$$\therefore \text{ Voltage regulation} = \frac{\binom{V_0}{\pi} - \binom{V_0}{\pi} - [((I_{dc})_{\text{full load}})(R_f + R_S)]}{\frac{V_0}{\pi} - ((I_{dc})_{\text{full load}})(R_f + R_S)}$$

$$=\frac{\left(\left(I_{dc}\right)_{full \ load}\right)\left(R_{f}+R_{S}\right)}{V_{0}/(\pi)-\left(\left(I_{dc}\right)_{full \ load}\right)\left(R_{f}+R_{S}\right)}$$

Thus the voltage regulation is v = y poor in half –wave rectifiers.

*Current rating of diode*: In a half wave rectifier, the dc diode current is equal to the dc load current. On the sheets,  $I_{dc}$  is usually listed as  $I_0$ , known as current rating of the diode; this tells us how much direct current the diode can handle. The diode must have current rating greater than the average rectified current.

The simple half-wave rectifier filters combination although gives D.C. voltage, it has got several disadvantages. The three major disadvantages are

- a. Its output changes with input A.C. supply voltage.

- b. Its output voltage changes with the amount of load current drawn.

- c. Ripple increases at higher load currents.

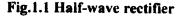

#### 1.4 Full-wave rectifier

. To utilize the total power content, and to reduce the ripple, we have to rectify the full-wave. This can be done in two ways;

1) A transformer with centre-tapped secondary and two diodes

2) four diodes arranged in a bridge form and a transformer

# 1.4.1 Full-wave rectifier using a transformer with centre-tapped secondary and two diodes:

The circuit is shown in Fig 1.2

Fig.1.2 Full-wave rectifier with two diodes

1

The circuit is essentially a combination of two half-wave rectifier circuits, each supplied from half of the transformer secondary. When the transformer output voltage is positive at the top, as illustrated in Fig.1.2., the anode of  $D_1$  is positive and the center-tap of the transformer is connected to the cathode of  $D_1$  via  $R_L$ .

Consequently,  $D_1$  is forward biased, and load current ( $I_L$ ) flows from the top of the transformer secondary though  $D_1$  through  $R_L$  from top to bottom and back to the transformer center-tap. During this time, the polarity of the voltage from the bottom half of the transformer secondary causes diode  $D_2$  to be reverse- biased.

For the duration of the negative half-cycle of the transformer output, the polarity of the transformer secondary voltage causes  $D_1$  to be reversed biased and  $D_2$  to be forward biased  $I_L$  flows from the bottom terminal of the transformer secondary through diode  $D_2$ , through  $R_L$  from top to bottom, and back to the transformer center-tap. The output waveform is the combination of the two half-cycles; that is, a continuous series of positive half-cycles of sinusoidal waveform. This is full wave rectification and the circuit is called a full-wave rectifier.

#### 1.4.2 Average current and voltage components of a full-wave rectifier:

As both the diodes are considered to be identical, also considering that the dynamic characteristic is linear for each diode, the mathematical analysis of full wave rectifier can be given as follows:

Let  $v = V_0$  since the applied alternating potential also considering that the dynamic forward resistance of each diode and  $R_s$  the resistance of the secondary of transformer. The instantaneous value of current through the load will be equal to the sum of the currents due to diodes  $D_1$  and  $D_2$  at that instant. These currents are given by the relations.

$|_{b2} = 0$

Also

IP1=0

$i_{b2} = \frac{V_0}{(R_f + R_s + R_L)} \sin(\omega t + \pi) = -I_0 \sin \omega t$

during  $\pi \leq \omega t \leq 2\pi$ ,

.....(1.4.1)

#### Average values:

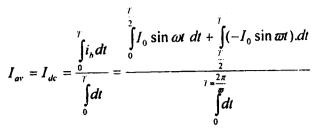

The average value of current (Idc) through RL can be given by

$$=\frac{2I_0}{\pi}=\frac{2V_0}{\pi(R_f+R_S+R_L)}$$

....(1.4.2)

So, the dc or average voltage at the load RL will be

$$V_{dc} = I_{dc}R_{L} = \frac{2I_{0}R_{L}}{\pi} = \frac{2V_{0}R_{L}}{\pi(R_{f} + R_{s} + R_{L})} = \frac{2V_{0}}{\pi[1 + (R_{f} + R_{s})/R_{L}]}$$

and  $P_{dc} = V_{dc}I_{dc} = I_{dc}^{2}R_{L} = \frac{4V_{0}^{2}R_{L}}{\pi^{2}[(R_{f} + R_{s} + R_{L})]^{2}]}$

rms value of current: The rms (or effective) value of current in the circuit can be given as

$$I_{rms}^{2} = \frac{1}{T} \left[ \int_{0}^{T/2} (i_{h1})^{2} dt + \int_{T/2}^{T} (i_{h2})^{2} dt \right]$$

$$I_{rms}^{2} = \frac{\int_{0}^{T} i_{h}^{2} dt}{\int_{0}^{T} dt} = \frac{\int_{0}^{T} \frac{\pi}{2} \int_{0}^{\pi} 2 \sin^{2} \omega t dt + \int_{2}^{\pi} \frac{\pi}{2} dt}{\int_{0}^{T} \frac{\pi}{2} \int_{0}^{\pi} \frac{\pi}$$

Or  $I_{rms} = I_0 / \sqrt{2} + \frac{V_0}{\sqrt{2}(R_f + R_s + R_L)}$  .....(1.4.3)

# 1.4.3 Harmonic components of rectified output

Frequency components of rectified output: Fourier analysis of the output waveform of the Full-wave rectifier will be having frequency components depending upon the resultant due to the waveform of each diode output

$$i_{b1} = I_0 \left[ \frac{1}{\pi} + \frac{1}{2} \sin \omega t - \frac{2}{3\pi} \cos 2\omega t - \frac{2}{15\pi} \cos 4\omega t \dots \right]$$

Since  $i_{b2}$  is 180° out of phase with  $i_{b1}$  and hence

$$i_{h1} = I_0 \left[ \frac{1}{\pi} - \frac{1}{2} \sin \omega t - \frac{2}{3\pi} \cos 2\omega t - \frac{2}{15\pi} \cos 4\omega t \dots \right]$$

Therefore the total current

$$i_{b} = I_{0} \left[ \frac{2}{\pi} - \frac{4}{3\pi} \cos 2\omega t - \frac{4}{15\pi} \cos 4\omega t \dots (1.4.4) \right]$$

This equation shows that a lowest frequency term has a frequency twice the frequency of the input source and the odd harmonics are not present.

#### **1.4.4 Other important parameters**

Rectifier efficiency: The percentage of efficiency is defined as

Ripple factor. The ripple factor is given by

PEAK INVERSE VOLTAGE: In the case of full-wave rectifier when one diode (say D<sub>1</sub>) is conducting, the other diode (D<sub>2</sub>) will be non- conducting. The kerchief's laws can be applied to fig, the equation obtained will be

$$v_{h1} - v_{h2} + 2V_0 \sin \omega t = 0$$

Where  $v_{b1}$  and  $v_{b2}$  are the potential drops across  $D_1$  and  $D_2$  respectively. If the diode D1 is conducting we can consider the potential drops across it as zero, hence the potential drops across non- conducting diode (D2) will be

$$v_{h2} = 2V_0 \sin \omega t$$

or  $(v_{h2})_{max} = 2V_0$

Similarly for the diode (D2) as conducting and (D1) non- conducting

$$v_{h1} = -2V_0 \sin \omega t \ or \ (v_{h1})_{max} = 2V_0$$

So the peak inverse voltage (PIV) for the diode used for full wave rectifier circuit is 2Vo, each diode must have sufficient insulation to with stand this voltage, or PIV rating greater than  $2V_0$ .

Voltage regulation: The Voltage regulation is given by

$$V.R. = \frac{(V_{dc})_{pol}}{(V_{dc})_{pull load}}$$

$(V_{dc}) = \frac{2V_0 R_L}{\pi (R_L + R_s + R_L)} = \frac{2V_0}{\pi} \left[ 1 + \frac{R_L + R_s}{R_L} \right]$

Here

Here we have assumed  $(R_T + R_S) < R_L$

At no load (open circuit  $R_L = \infty$ ),  $I_{dc} = 0$ , and  $V_{dc} = 2V_0/\pi$ . At full load we have,

Current rating of diodes: The current rating of each diode Io must be greater than half the dc load current.

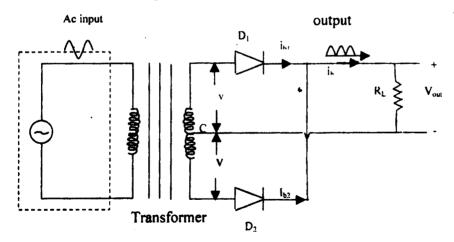

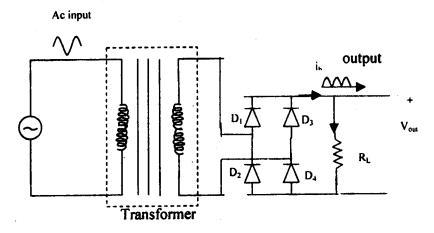

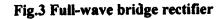

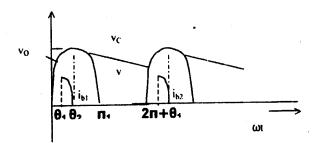

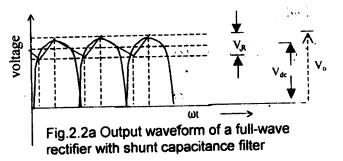

1.5 Full-wave rectifier using diode bridge:

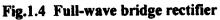

The center-tapped transformer used in the circuit of Figs.1 and 2 is usually more expensive and requires more space than additional diodes. So, a bridge rectifier is the mot most frequently used for full-wave rectification. The bridge rectifier circuit shown in Fig.1.3 consists of four diodes connected with their arrowhead all pointing toward the positive output terminal of the circuit. Diodes D<sub>1</sub> and D<sub>2</sub> are series-connected, as are D<sub>3</sub> and D<sub>4</sub>. The ac input terminals are the junction of D<sub>1</sub> and D<sub>2</sub> and the junction of D<sub>3</sub> and D<sub>4</sub>. The positive output terminal is at the cathodes of D<sub>1</sub> and D<sub>3</sub>, and the negative output is at the anodes of D<sub>2</sub> and D<sub>4</sub>.

During the positive half-cycle of input voltage, diodes  $D_1$  and  $D_4$  are in series with  $R_L$ . Thus load current ( $I_L$ ) flows from the positive input terminal through  $D_1$  to  $R_L$ , and then through  $R_L$  and  $D_4$  back to the negative input terminal. Note that the direction of the load current through  $R_L$  is from top to the three negative output is positive input terminal is applied to the cathode of  $D_2$ , and the negative output is at  $D_2$  anode. So,  $D_2$  is reverse biased during the positive half-cycle of the input. Similarly,  $D_3$  has the negative input at its anode and the positive output at its cuthode during the positive input half-cycle, causing  $D_3$  to be reverse biased. The diodes  $D_2$  and  $D_3$  are forward biased during the negative half-cycle of the input waveform, while  $D_1$  and  $D_4$  are reverse biased. Although the circuit input terminal polarity is reversed,  $I_L$  again flows through  $R_L$  from top to bottom, via  $D_3$  and  $D_2$ .

In Fig 1.4, the bridge circuit is drawn in the conventional form which is seen in various text books. The working is same. It will be easy to remember the diode bridge arrangement, if we follow the Fig1.3.

It is seen that during both half-cycles of the input, the output terminal polarity is always positive at the top of  $R_L$ , negative at the bottom. Both positive and negative half-cycles of the input are passed to the output. The negative half-cycles are invarted, so that the output is a continuous series of positive half-cycles of sinusoidal voltage.

The bridge rectifier has two forward-biased diodes in series with the supply voltage and the load. Because each diode has a forward drop ( $V_F$ ), the peak output voltage is.

$$V_{po} = V_{pi} - 2V_F$$

As in the case of the half-wave rectifier. A reservoir capacitor substantially changes the full-wave rectified output voltage waveform and affects the diode current and voltage requirements.

# **1.5.1 Average current and voltage components of a full-wave bridge rectifier** Instantaneous currents through the load R<sub>L</sub> will be given as

$|_{b2} = 0$

and Also

|<sub>b1</sub>=0

$$i_{h2} = \frac{V_0}{(2R_f + R_S + R_L)} \sin(\omega t + \pi) = -I_0 \sin \omega t$$

during  $\pi \leq \omega t \leq 2\pi$ ,

Thus the maximum current through the load is

$$\frac{V_0}{(2R_1+R_S+R_L)}\sin(\omega t)=I_0$$

The expressions for the average dc, r.m.s value of current, rectifier efficiency and ripple factor may be obtained as for the full-wave rectifier.

$$I_{ik} = \frac{2I_0}{\pi} = \frac{2V_0}{\pi(2R_f + R_s + R_L)},$$

$$V_{dk} = \frac{2V_0}{\pi[1 + (2R_f + R_s)/R_L]},$$

$$I_{rms} = \frac{V_0}{\sqrt{2}(2R_f + R_s + R_L)},$$

% of  $\eta = \frac{81.2}{[1 + (2R_f + R_s)/R_L]}$

And r = 0.48

The peak inverse voltage across each diode is the peak voltage ( $V_0$ ) across the secondary of transformer instead of  $2V_0$ , the PIV value for full-wave rectifier.

#### 1.5.2 Advantages and disadvantages of bridge rectifier

- 1. Small transformer can be used.

- 19 Central tap on the secondary of the transformer is not required.

- 2:○ PIV per diode is V₀ instead of 2V₀ in a full-wave rectifier.

The main disadvantages of this type of rectifier are

- 1. The circuit requires two extra diodes, and

- 2. It has a poor voltage regulation.

#### 1.5.3 Peak loss

An aspect of most rectification is a loss from peak input voltage to the peak output voltage, caused by the built-in voltage of the diodes (around 0.7 V for ordinary silicon p-n-junction diodes and 0.3 V for Schottky diodes). Half-wave rectification and full-wave rectification using two separate secondary windings will have a peak voltage loss of one diode drop. Bridge rectification will have a loss of two diode drops. This may represent significant power loss in very low voltage supplies. In addition, the diodes will not conduct below this voltage, so the circuit is only passing current through for a portion of each half-cycle, causing short segments of zero voltage to appear between each "hump".

#### 1.5.4 Comparison of half-wave and full-wave rectifiers

- 1. In half -wave rectifier, the current flows through the secondary of the transformer always in the same direction, the dc saturation of the transformer core takes place. This produces hysteresis loss and harmonics in the secondary output and reduces the efficiency of transformer. In a full-wave rectifier equal currents flows through the two halves of the center tapped secondary of the transformer in opposite directions and hence no core saturation exists.

- 2. The average or dc values of currents and voltages are double in case of full-wave in comparison of half -wave rectifier.

- 3. Effective or r.m.s value of output current in full-wave rectifier is  $\wp$  times the value for half -wave rectifier.

- 4. The dc power delivered to the load by a full-wave rectifier is 4 times the power delivered by a half-wave rectifier.

- 5. The fundamental angular frequency term is eliminated in full-wave rectifier secondary harmonics component  $(2\omega)$  in the output of full-wave rectifier is easier to filter out.

- 6. Efficiency of full-wave rectifier is twice that of half -wave rectifier.

- 7. The ripple factor of full-wave rectifier is quite low (0.48) than of a half -wave rectifier (1.21). The full-wave rectifier converts higher percentage of power

into desired dc power with smaller portions as undesired ac. So for a haif wave rectifier a comparatively expensive smoothing filter is required.

- The full-wave rectifier diode must be chosen such that is insulation strength is sufficient to withstand the peak inverse voltage of 2V<sub>0</sub>. PIV is V<sub>0</sub> only for a diode of half -wave rectifier.

- 9. The half -wave rectifier has poor voltage regulation in comparison to a full-wave, i.e. the change in the output of a full-wave is smaller than that or a half -wave rectifier. The half -wave rectifier has the chief advantage of simplicity and low design cost and PIV value compared to a full-wave rectifier. But the above points clearly indicate that a full-wave rectifier has higher efficiency, higher dc output values, less core saturation, less ripple factor and higher voltage regulation. So for a better rectification full-wave rectifier is always preferred than a half-wave rectifier.

### 1.6 SUMMARY

Most of the present day electronic units work on D.C. Power supply. Transistor based circuits need operating voltage in the range between 0 to  $\pm 30V$ . Linear IC based circuits need  $\pm 15VD$ .C. Digital I.C  $\_a$ sed circuits need  $\pm 5V$ . So, it is very essential to know how to build a D.C voltage source from A.C mains supply.

A D.C. Power supply can be constructed in three ways.

- 1. Simple unregulated power supply with filter circuit.

- 2. Transistor or I.C based Regulated power supply

3. Switching Mode power supply

Simple unregulated power supply is used in low-cost commercial electronic items Transistor or I.C based Regulated power supply are used in laboratory and scientific electronic equipment.

An unregulated power supply is one that simply converts the A.C. voltage taken from the A.C. Supply into required D.C. voltage supply at the required current. It consists of the following parts:

1. Step down Transformer

- 2. Rectifier

- 3. Filter circuit

The maximum efficiency of a half-wave rectifier will be 40.6%. But the rectifier delivers maximum output power when the load resistance is equal to  $R_f$ , the efficiency is now reduced to 20.3 percent only. The effective values of the ac components of the output exceed the dc value of the output. So, the half-wave rectifier is not a suitable device for obtaining dc.

Voltage regulation is a measure of the ability of a rectifier to maintain a specified output voltage with the variation of load resistance and is defined as

Voltage regulation(V.R.) =  $\frac{output at no load - output at full load}{output at full load}$

voltage regulation is very poor in half-wave rectifiers.

Ripple factor is defined as the ratio of the effective value of the ac components of the current or voltage to the direct or average value of the current or voltage i.e.

Ripple factor(r) =  $\frac{effective \ value \ of \ ac \ components}{dc \ value \ of \ the \ components}$

A full-wave rectifier can be formed by

1. A step-down transformer with centre-tapped secondary and two diodes.

2 Four diodes arranged in a bridge form and a step-down transformer.

The output waveform of a full-wave rectifier is a continuous series of positive halfcycles of sinusoidal waveform.

The bridge rectifier has two forward-biased diodes in series with the supply voltage and the load. Because each diode has a forward drop ( $V_F$ ), the peak output voltage is,

$$V_{po} = V_{pi} - 2V_F$$

For a given tolerable ripple the required capacitor size is proportional to the load current and inversely proportional to the supply frequency and the number of output peaks of the rectifier per input cycle. The load current and the supply frequency are generally outside the control of the designer of the rectifier system but the number of peaks per input cycle can be affected by the choice of rectifier design.

A half-wave rectifier will only give one peak per cycle and for this and other reasons is only used in very small power supplies. A full wave rectifier achieves two peaks per cycle and this is the best that can be done with single-phase input.

#### 1.7 KEY TERMINOLOGY

Regulation: Keeping a parameter to be in set limits irrespective of the other parameters that otherwise cause changes in the first parameter

**Unregulated D.C. power supply:** A D.C. supply that has no mechanism to keep its output voltage at a constant value when changes in load current or input supply value changes.

**Rectifier:** A rectifier is a diode. There are two types of rectifiers. 1) Signal rectifier 2) Power supply rectifier. Even though basically both the types perform the same task, a signal diode is used to rectify modulated r.f waves to recover the modulated signal or for demodulation .A diode meant for use as a rectifier in power supply will have large current carrying capacity and large reverse break down voltage.

#### 1.8 Self assessment Questions:

#### Long answer Questicas

- 1. What is a rentifier?. Explain the working of a full-wave rectifier. Obtain expression for verage and RMS values of current and efficiency.

- 2. Describe the working of a full-wave rectifier with centre tapped transformer.

- 3. Describe the working of a full-wave rectifier and obtain expression for efficiency.

- 4. Explain the circuit diagram of a bridge rectifier and explain its operation with waveforms. Derive expressions for its efficiency and ripple factor.

A half-wave rectifier uses silicon diode with a forward resistance of 0.05 ohms and a threshold voltage of 0.7 Volt. It has a secondary emf of 14.4 Volts(r.m.s) with a resistance of 0.2 ohms. For a load resistance of 15 ohms calculate

i) dc load current, ii) dc load voltage, III) voltage regulation and IV) efficiency.

#### Short answer questions

- 1. The dc output voltage is 40 Volts at full load and 41 Volts with out any load current. calculate the load regulation factor in percent

- 2. If the output voltage of a centre tap full-wave rectifier is 100V. Determine the peak inverse voltage.

- 3. Explain about  $\pi$  section filter.

- 4. Compare half and full-wave rectifiers

- 5. A full-wave rectifier delivers 50W to a load of 2000hms. If the ripple factor is 2%, calculate the a.c. ripple voltage across the load.

- 6. A half wave rectifier uses a transformer of turns ratio 8:1. If the primary voltage is 230V (r.m.s), find (i) dc output voltage,(ii) peak inverse voltage.

- 7. A full-wave rectifier uses a centre-tapped transformer. The ac voltage from its centre tap to either end is 10 sin 314t. The load resistance of the circuit is  $40\Omega$  and diode resistance  $10\Omega$ . Find  $I_{dc}$ ,  $I_{ms}$ , ripple factor and efficiency.

An ac supply of 230V, 50Hz is applied to bridge type full-wave rectifier circuit through a transformer of turns ratio 4:1. Assuming the diodes to be ideal and resistance R<sub>L</sub>= 200 Ω, find i) dc output voltage, peak inverse voltage, output efficiency.

## **1.9 Text and Reference Books:**

- 1. Integrated Electronics by Millman and Halkias

- 2. Basic Electronics and Linear Circuits Bhargava etc

# **REFERENCE BOOKS**

- 1. A text lab manual in Electronics by ZBAR (Tata Mc graw Hill)

- 2. Electronics fundamentals by JD Ryder

- 3. Electronic Devices and Circuits by Samuel Seely.

# **D.C.POWER SUPPLY WITH VARIOUS FILTERS**

#### **OBJECTIVES OF THE LESSON**

To learn about the effect of filters on the performance of power supplies.

#### **STRUCTURE OF THE LESSON**

2.1 Introduction

2.2 Half-wave rectifier with shunt capacitor filter

2.3 Full-wave rectifier with shunt capacitor filter

2.4 Full-wave bridge rectifier with shunt capacitor filter

2.5 Half-wave rectifier with series inductance filter

2.6 Full-wave rectifier (with two diodes and) with series inductance filter

2.7 Full-wave rectifier (with two diodes and) with L-section series inductance filter

2.8 II-section filter or capacitor input filter

2.9 Summar /

2.10 Key terminology

2.11 Self assessment Questions

2.12 Text and Reference Books

#### 2.1 INTRODUCTION

While half-wave and full-wave rectification suffice to deliver a form of DC output, neither produces constant-voltage DC. The ripple is 121% in the output of the half - wave rectifier, and 48%, in the full-wave rectifier. This large amount of ripple can not be tolerated especially in power supplies. The unwanted ac-components of the output can be filtered using filter circuits discussed in our first year course.

To smooth the output voltage of rectifiers, filter circuits (also know as smoothing circuits) are used. There are the various combinations of the capacitors and inductors. These are low pass filters.

The most common arrangements  $Q_{1}^{t}$  filter used are: (a) shunt capacitor b) series inductor (c) L-section and (d).  $\Pi$ -section filters.

#### 2.2 Half-wave rectifier with shunt capacitor filter:

A capacitor connected in parallel with the load resistance serves, effectively as a filter for ac components. The simple circuit filter-capacitor filter half-wave rectifier is shown in Fig.2.1. The reactance offered by capacitor  $X_c = 1/\omega C$ , so for dc ( $\omega = 0$ ),

#### UNIT I

it offers an infinite resistance, while for any frequency (ac), its value decreases with increase in frequency. So, if the resistance due to capacitor is very small in comparison of load resistance (i.e.,  $1/\omega C << R_L$ ), then most of the ac or harmonic components will bypass through capacitor and will not appear through  $R_L$ . This will improve the D.C. output.

Fig 2.1 Half-wave rectifier with shunt capacitance filter

Fig: 2.1a Output wave form of a halfwave rectifier with shunt capacitance

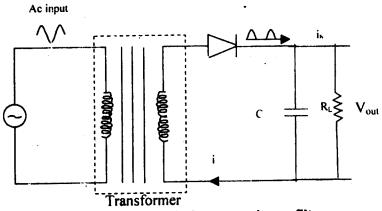

During the first quarter cycle of ac source voltage, the diode is forwardbiased, it charges the capacitor to the peak voltage V<sub>0</sub>. Just past the peak, the diode gets reverse biased and stops conducting. It is because the source is slightly less than V<sub>0</sub> the voltage across the capacitor. Now the voltage across the capacitor decreases exponentially due to its discharging through the lead resistance R<sub>L</sub>. The C and R<sub>L</sub> are so chosen that the time constant ( $\tau = GR_L$ ) is much greater than the period T of the input signal. Thus the capacitor will lose only a small part of charge, during the time diode remains reversed biased or in the off position. Therefore the fall in potential at the load will be small. During the next positive half cycle, the diode will conduct again when the input voltage exceeds the capacitor voltage. Thus the capacitor will be recharged to the peak voltage.

The diode conduction (current flow) will be only for a short period  $(\theta_1 + \theta_2)$  and that too in the form of pulse and from  $\theta_2$  to  $(2\pi + \theta_1)$  the discharge of capacitor will take place. During this discharge the source is disconnected; so, the diode acts as an automatic switch. Thus we see that the charge lost by the capacitor during each cycle is replenished periodically by the current pulses.

During the charging interval  $i_b = i_c + i_R$  and since the diode switch is closed, the supply voltage  $v = V_p \sin \omega t$ , hence

During the conducting interval, one can assume  $v_{c} = v = V_{0} \sin \omega t$ , therefore

$i_{b} = \omega C V_{0} \cos \omega t + (V_{0} / R_{1}) \sin \omega t \qquad \omega t_{1} < \omega t < \omega t_{2}$   $i_{b} = \frac{V_{0}}{R_{1}} \sqrt{(1 + \omega^{2} R_{1}^{2} C^{2})} \sin(\omega t + \phi) \qquad \text{where } \phi = \tan^{-1} \omega R_{1} C.$

At

$$\omega t = \theta_2$$

,  $i_b = 0$  and we have

$\omega CV_0 \cos \theta_2 + (V_0 / R_L) \sin \theta_2 = 0$  or  $\theta_2 = \tan^{-1}(-\omega R_L C)$

$\phi = \tan^{-1}(\omega R_L C) = \pi - \tan^{-1}(-\omega R_L C) = \pi - \theta_2$

and  $i_b = \frac{V_0}{R_L} \sqrt{(1 + \omega^2 R_L^2 C^2)} \sin(\omega t_2 + \omega t)$   $\omega t_1 < \omega t < \omega t_2$ .

For the period between  $\omega t$  to  $2\pi + \omega t_1$ , the rectifier is not conducting i.e.,  $i_b = 0$  and solution of Eq.2.2.1 becomes

$$\mathbf{v}_{i} = \mathbf{A} \mathbf{e}^{-i \cdot \mathbf{R}_{i} \mathbf{C}}$$

$\omega t = \omega t_2, v_c = V_0 \sin \omega r_2$ , hence we have

$\omega C V_0 \cos \theta_2 + (V_0 / R_L) \sin \theta_2 = 0$  or  $\theta_2 = \tan^{-1} (-\omega R_L C)$

$$\phi = \tan^{-1}(\omega R_L C) = \pi - \tan^{-1}(-\omega R_L C) = \pi - \theta_2$$

and  $\mathbf{i}_b = \frac{\mathbf{V}_0}{R_L} \sqrt{(\mathbf{I} + \omega^2 R_L^2 C^2)} \sin(\omega t_2 + \omega t) \quad \omega \mathbf{t}_1 < \omega \mathbf{t} < \omega \mathbf{t}_2$

For the period between  $\omega t$  to  $2\pi + \omega t_1$ , the rectifier is not conducting i.e.  $i_h = 0$  and solution of Eq. 2.2.1 becomes

$$\mathbf{v}_{c} = A e^{-t - R_{c} C}$$

At

$$\omega t = \omega t_2, v_c = V_0 \sin \omega t_2$$

, hence we have

$$v_{C} = V_0 \sin \omega t_2 e^{-(\omega_1 - \omega t_2)/(\omega t_1 C)} \qquad \omega t_2 < \omega t < (2\pi + \omega t_1).$$

At  $\omega t = \omega t_1 + 2\pi$ ,  $v_C = V_0 \sin \omega t_1$ , hence we have

$$\sin \omega t_1 = \sin \omega t_2 e^{-(\omega t_1 + 2\pi - \omega t_2)/\omega k_1 t}$$

This relation shows that  $\omega t_2$  decreases and  $\omega t_1$  increase with  $\omega R_L C$  i.e., the conduction angle is short for large values of capacitance. The dc voltage across the load can be calculated by averaging the capacitor voltage  $v_c$  over a cycle, as

$$V_{dc} = \frac{1}{2\pi} \int_{\omega_1}^{\omega_2} V_0 \sin \omega t \, d(\omega t) + \frac{1}{2\pi} \int_{\omega_2}^{2\pi + \omega_1} V_0 \sin \omega t \, e^{-(\omega t - \omega t_2)/\omega R_L C_d} (\omega t).$$

After integrating and substituting the values from eqs and , we get

$$V_{dc} = \frac{V_0}{2\pi} \sqrt{(1 + \omega^2 R_L^2 C^2)} [1 - \cos(\omega t_2 - \omega t_1)], \qquad (2.2.3)$$

This relation shows that  $V_{dc} = V_0 / 2\pi$  for low values of capacitance and reaches to the peak value of the voltage for large values of capacitance. High value of  $\omega R_L C$  is needed for a small ripple.

# 2.3 Full-wave rectifier with shunt capacitor filter

The operation of the full wave circuit is similar to that of the half wave circuit with the discharge time of the capacitor running only to  $\pi + \omega t_1$  instead  $2\pi + \omega t_1$ . The cut in angle can be recalculated by the use of  $\pi$  in place of  $2\pi$ .

2.5

$$\sin \omega t_1 = \sin \omega t_2 e^{-(\omega t_1 + 2\pi - \omega t_2)/(\omega k_1 C)}$$

The dc voltage can be calculated by averaging the capacitor voltages from  $\omega_1$  to  $\pi + \omega_1$  and noting that there are two such pulses per cycle.

$$V_{dc} = \frac{V_0}{\pi} \sqrt{\left(1 + \omega^2 R_L^2 C^2\right)} \left[ \left(1 - \cos(\omega t_2 - \omega t_1)\right) \right]$$

(2.3.1)

Thus the variations in  $V_{dc}$  by the load resistance  $R_L$  are much smaller for the fullwave rectifier than for the half-wave rectifier i.e., the voltage regulation is better for the full-wave circuit.

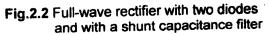

Because of complex wave forms, the output wave is taken to be a triangular waveform for nearest approximate calculations. There are made of portions of straight lines, as shown in Fig.2.2a, peak value  $V_0$  (maximum voltage at the capacitor). E<sub>R</sub> is the fall in voltage across the capacitor at the load. So, the average or dc value of potential for such output is given by

$$V_{dc} = V_0 - V_R / 2. \tag{2.3.2}$$

The rms value of triangular ripple wave is given by

$$V_{\rm raw} = V_{\rm R} / 2\sqrt{3}.$$

(2.3.3)

i.e., the rms value of the ripple component of the triangular wave depends on the peak value ( $V_R$ ) of wave and independent of slope or length of the straight lines.

$t_{dc}$  = rate of loss of charge from capacitor = loss of charge due to a drop in potential (V<sub>R</sub>) divided by T/2, i.e., half period

$$\therefore I_{dc} = 2CV_R / T = 2C.f.V_R.(as f is the frequency)$$

(2.3.4)

So, dc potential across the load RL is given by

$$V_{de} = I_{de} R_{L} = 2C f V_{R} R_{L}$$

(2.3.5)

The ripple factor is given as

$$r = \frac{V_{mis}}{V_{lx}} = \frac{V_R F 2\sqrt{3}}{2C f V_R R_L} = \frac{1}{4\sqrt{3} f R_L C}.$$

(2.3.6)

This shows that ripple factor raises inversely as time constant  $R_LC$ . Then the ripples will be smoothed when the value of C or  $R_L$  is high and shunt capacitor filter is only suitable for low output currents.

As  $I_{de} = 2CfV_R$  or  $V_R = I_{de}/2Cf$ .

Therefore, the output voltage

$V_{dc} = V_0 - I_{dc} / 4Cf$ . or  $V_{dc} = V_0 (1 + 1/4 fCR_1)^{-1}$

This relation shows that the output potential falls linearly with the increase in direct current and a simple capacitor filter will posses a poor regulation unless we have high value of the capacitor C. Thus, the regulation of series inductor is better than that of the shunt capacitor filter.

Shunt capacitor is known as a **reservoir capacitor**, **filter capacitor** or **smoothing capacitor**, is placed at the DC output of the rectifier. There will still remain an amount of AC ripple voltage and the voltage is not completely smoothed. Sizing of the capacitor represents a tradeoff. For a given load, a larger capacitor will reduce ripple but will cost more and will create higher peak currents in the transformer secondary and in the supply feeding it. In extreme cases, where many rectifiers are loaded onto a power distribution circuit, it may prove difficult for the power distribution authority to maintain a correctly shaped sinusoidal voltage curve.

## 2.4 Full-wave Bridge rectifier with shunt capacitance filter

For many applications, especially with single phase AC, where the full-wave bridge serves to convert an AC input into a DC output, the addition of a capacitor may be important because the bridge alone supplies an output voltage of fixed polarity but pulsating magnitude

The function of this capacitor, known as a reservoir capacitor is to lessen the variation in (or 'smooth') the rectified AC output voltage waveform from the bridge. One explanation of 'smoothing' is that the capacitor provides a low impedance path to the AC component of the output, reducing the AC voltage across, and AC current through, the resistive load. In less technical terms, any drop in the output, voltage and current of the bridge tends to be cancelled by loss of charge in the capacitor. This charge flows out as additional current through the load. Thus the change of load current and voltage is reduced relative to what would occur without the capacitor. Increases of voltage correspondingly store excess charge in the capacitor, thus moderating the change in output voltage / current.

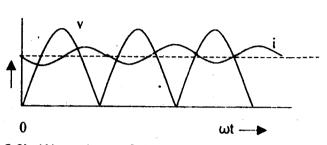

The idealized waveforms shown above are seen for both voltage and current when the load on the bridge is resistive. When the load includes a smoothing capacitor, both the voltage and the current waveforms will be greatly changed.

2.7

on full wave rectifier output

While the voltage is smoothed, as described above, current will flow through the **bridge** only during the time when the input voltage is greater than the capacitor **voltage**. For example, if the load draws an average current of n Amps, and the diodes conduct for 10% of the time, the average diode current during conduction must be 10n Amps. This non-sinusoidal current leads to harmonic distortion and a poor power factor in the AC supply.

In a practical circuit, when a capacitor is directly connected to the output of a bridge, the bridge diodes must be sized to withstand the current surge that occurs when the power is turned on at the peak of the AC voltage and the capacitor is fully discharged. Sometimes a small series resistor is included before the capacitor to limit this current, though in most applications the power supply transformer's resistance is already sufficient.

Precautions to be taken in using a D.C. Power supply with shunt capacitance filter:

The simplified circuit shown in Fig.2.3 has a well deserved reputation for being dangerous, because, in some applications, the capacitor can retain a lethal charge

after the AC power source is removed. If supplying a dangerous voltage, a practical circuit should include a reliable way to safely discharge the capacitor. If the normal load can not be guaranteed to perform this function, perhaps because it can be disconnected, the circuit should include a bleeder resistor connected as close as practical across the capacitor. This resistor should consume a current large enough to discharge the capacitor in a reasonable time, but small enough to minimize unnecessary power waste.

Because a bleeder sets a minimum current drain, the regulation of the circuit, defined as percentage voltage change from minimum to maximum load, is improved. However in many cases the improvement is of insignificant magnitude.

The capacitor and the load resistance have a typical time constant T = RC where C and R are the capacitance and load resistance respectively. As long as the load resistor is large enough so that this time constant is much longer than the time of one ripple cycle, the above configuration will produce a smoothed DC voltage across the load.

In some designs, a series resistor at the load side of the capacitor is added. The smoothing can then be improved by adding additional stages of capacitor-resistor pairs, often done only for sub-supplies to critical high-gain circuits that tend to be sensitive to supply voltage noise.

In a practical circuit, when a capacitor is directly connected to the output of a bridge, the bridge diodes must be sized to withstand the current surge that occurs when the power is turned on at the peak of the AC voltage and the capacitor is fully discharged. Sometimes a small series resistor is included before the capacitor to limit this current, though in most applications the power supply transformer's resistance is already sufficient.

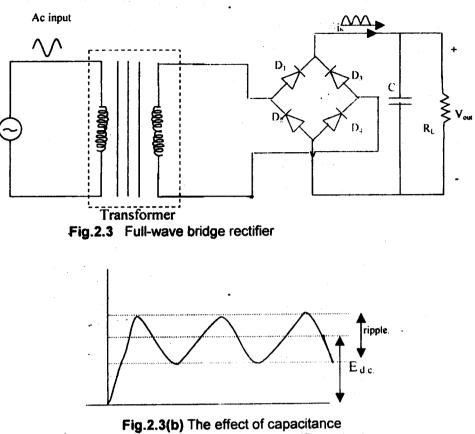

### 2.5 Half-wave rectifier with Series inductance filter

A filter circuit can also be formed by connecting a choke (inductor) in series with the load R<sub>L</sub>. The inductance (L) of choke is quite high than its resistance (r<sub>L</sub>). In order to maintain a high value of L for a wide variation in current flow, some chokes use an iron core with a small air gap to prevent saturation. The inductor offers a high series impedance  $Z = r_L^2 + \omega^2 L^2$  in path of ac or harmonic components and opposes any change of current passing through it. Actually an inductor stores the energy in the form of magnetic filed when the current raises from the average value and thus reduces the ripples from the output. The Fig.2.4a shows the circuit diagrams of a half-wave with the series inductor filter. If  $v = V_0 \sin \omega t$  is the applied input at the diode, the output without filter will be as shown by dotted curves. In the case of half-wave rectifier with series inductor, the growth of current exists from 0 to  $\pi/2$  part of the output which is opposed by the inductance coil and from  $\pi/2$  to 0 there is a fall in current which is not allowed by the coil  $\frac{Ac input}{2}$

Fig 2.4a Half-waye rectifier with series inductance filter

**Fig.2.4b** Wave shape of the output voltage and current in a half-wave rectifier with series Inductance filter

So period of the current conduction is increased from 0 to  $\pi$  to 0 to  $(\pi+\theta_2)$ .  $\theta_2$  is known as *cut-off angle* and its value increase with the increase in L. Thus the gap of  $\pi$  to  $2\pi$  part of the cycle in the output has been filled to some extent by introducing a series inductor in the circuit due to the induced e.m.f.

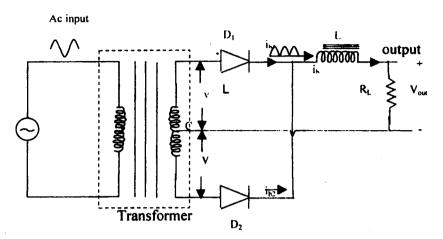

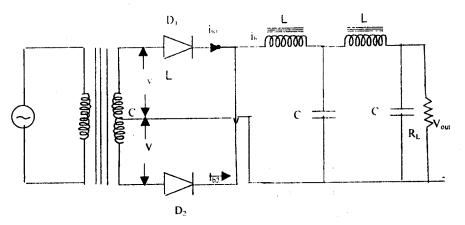

# 2.6 Full-wave rectifier (with two diodes and) with series inductance filter

Ţ

In the case of full-wave rectifier, the period of conduction in the second rectifier will start before the current in first has ceased. Thus the currents through the

inductor and load resistance never drops to zero, as shown by continuous curve in Fig.2.5(b)

Fig.2.5a Full-wave rectifier (with two diodes) with series Inductance filter

Fig.2.5b Wave shape of the output voltage and current in a full-wave rectifier with series Inductance filter

dc output. Fourier analysis of the output waveform for full-wave rectifier is given by

$$v = \frac{2V_0}{\pi} \left[ 1 - \frac{2}{3} \cos 2\omega t - \frac{2}{15} \cos 4\omega t \right]$$

(2.6.1)

The first term is the dc component of the input filter voltage.

Assume that  $R_s$  the resistance of the secondary of transformer and  $R_f$  the dynamic forward resistance of each diode are negligible. If  $r_L$  be the resistance of inductor (or choke) and  $R_L$  is load resistance, then the (dc) current through and voltage across the load can be given as

ŧ

$$I_{de} = \frac{2V_0}{\pi(r_1 + R_1)} = \frac{2V_0}{\pi(R_1)}, (lf r_1 << R_1)$$

(2.6.2)

and

$$V_{dc} = I_{dc}R_L = \frac{2V_cR_L}{\pi(r_L + R_L)} = \frac{2V_0}{\pi} = 0.637V_0, (lf r_c \ll R_L)$$

As  $r_{L}$  will always be quite small than the load resistance  $R_{L}$ ,

$$V_{d_{u}} = \frac{2V_{0}}{\pi} \left( 1 + \frac{r_{L}}{R_{L}} \right)^{-1} = \frac{2V_{0}}{\pi} \left( 1 + \frac{r_{L}}{R_{L}} \right)$$

$$= \frac{2V_{0}}{\pi} \frac{2V_{0}r_{L}}{\pi(R_{L})} = \frac{2V_{0}}{\pi} \frac{1}{\pi(R_{L})}$$

(2.6.3)

Voltage regulation: when there is no load  $I_{dc}$  is zero, and  $(V_{dc})_{nc} \xrightarrow{1}{2} 2V_0/\pi$ , therefore the voltage regulation.

$$V.R. = \frac{(!_{dc})_{icc,local} - (V_{dc})_{f,ill,local}}{(V_{dc})_{f,ill,local}} = \frac{(I_{dc})r_{l}}{(2V_{S}/\pi) - (I_{dc})r_{l}}$$

(2.6.4)

As the inductor (or choke) resistance is quite small, hence the regulation factor is also reduced, which means a better regulation.

**Ripple factor:** As the amplitudes of the higher harmonic terms are very small, hence their effects for producing ripple will also be very small, so only first ac component, i.e.,  $(2V_0/\pi)(\Box \cos 2\omega t)$  is used for calculation of ripple factor. While neglecting higher harmonic terms, we have considered that the impedance due to inductance at high frequencies was also high and thus there was a better filtration for these terms. From the elementary circuit theory we can write the alternating current through the load resistance R<sub>L</sub> as

$$I_{\alpha \kappa} = \frac{4V_0}{3\pi} \cdot \frac{\cos(2\omega t - \phi)}{\left[ R_1^2 + (2\omega L)^2 \right]^{1/2}}$$

(2.6.5)

Where  $R_1 = (r_L + R_L)$  and  $\phi = \tan^{-1}(2\omega L / R_1)$ . This is the angle by which the current lags behind the alternating voltage.

Thus the effective or rms value of ac at the output can be written as

$$I_{rms} = \frac{4V_0}{3\pi\sqrt{2}[R_1^2 + (2\omega L)^2]^{1/2}},$$

Hence ripple factor  $r = I'_{rms} / I_{de}$

$$=\left[\frac{4V_{0}}{3\pi\sqrt{2}[R_{1}^{2}+(2\omega L)^{2}]^{1/2}}\left|\left(\frac{2V_{0}}{\pi R_{1}}\right)^{-1}\right|\right]$$

$$=\frac{\sqrt{2}}{3\pi}\frac{1}{\sqrt{\left[1+\left\{2\omega L/(r_{L}+R_{L})\right\}^{2}\right]}}$$

(2.6.6)

From this equation, we have

- 1. If  $(r_L+R_L)$ >>2 $\omega$ L, the ratio 2 $\omega$ L/ $(r_L+R_L)$  can be neglected in comparison to1. so  $r = \omega/3 = 0.471$ , it was 0.48 for without filter, so under such a condition the filtering is poor.

- 2. if  $2\omega L >> (r_L + R_L)$ , so 1 can be neglected in comparison to the ratio (  $2\omega L/R_1$ )<sup>2</sup> in the denominator, so

$$r = \frac{\sqrt{2} (r_{L} + R_{L})}{3\pi 2\omega L} = 0.236 \frac{(r_{L} + R_{L})}{\omega L}$$

(2.6.7)

This shows that r can be decreased by using a choke coil with high inductance and low resistance. Being  $\omega$  in the denominator, the higher frequencies will have less ripple factor. The ripple factor decreases as we decrease RL or increase load current.

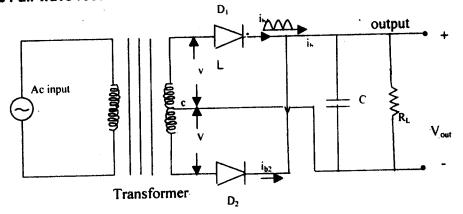

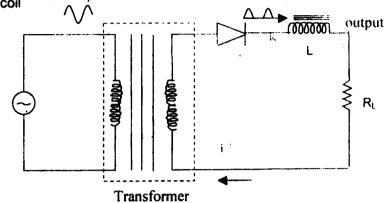

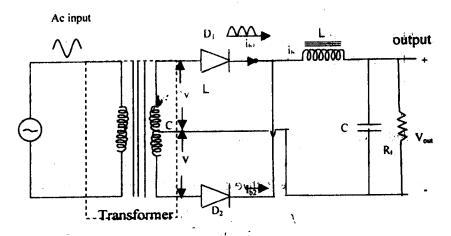

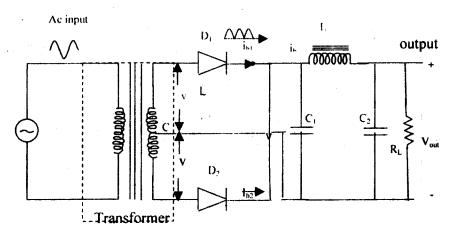

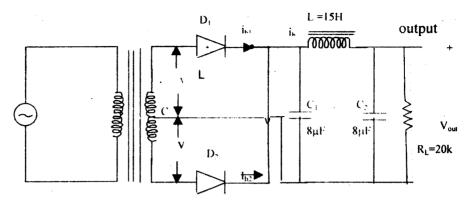

# 2.7 Full-wave rectifier (with two diodes and) with L-section series inductance filter:

The L-section or Inductor input Filter: This type of filter is the combination of Series Inductor and the shunt capacitor filters. It gives very low value of ripples at all loads and hence used frequently in the electronic equipments. The circuit for full wave L-section filter is shown in Fig.2.6a

Fig 2.6a: Full-wave rectifier with two diodes with L-section filter

The Inductor L offers a high impedance to the ac or harmonic components and thus reduces there components from the output. The shunt capacitor bypasses the ac

components around the load. Thus the ripples in output are reduced considerably. The dc voltage and ripple factor may be calculated by taking the first two terms in the Fourier series representation of the output voltage of full-wave rectifier as

(2.7.1)

$v = \left(\frac{2V_0}{\pi}\right) - \left(\frac{4V_0}{3\pi}\right) \cos 2\omega t \; .$

Fig.2.6b Wave shape of the output voltage and current in a full wave rectifier with series Inductance filter

It is equivalent to a dc source in series with an ac source having twice the power line frequency. It the sum of the resistances of diode, secondary of transformer, choke is negligible and the load resistance is  $R_L$  then

$$V_{ak} = \frac{V_0}{\pi} - I_{ak} R_{l.}$$

(2.7.2)

The values of  $X_L$  and  $X_C$  at second harmonic of supply frequency (i.e., for a supply frequency  $\omega$ ) are  $2\omega L$  and  $1/2\omega C$  respectively. The Input impedance of the filter circuit at the second harmonic frequency  $2\omega$  is

$$Z_2 = 2j\omega L - \frac{jR_L 2\omega C}{R_L - j/2\omega C} \quad OR \quad |Z_2| = (4\omega^2 L C - 1)/2\omega C$$

The second harmonic e.m.f allows the ac current in the inductor L, given as

$$(I_L)_{rms} = \frac{4V_0}{3\sqrt{2\pi}} \cdot \frac{1}{Z_2} = \frac{8\omega CV_0}{3\pi\sqrt{2} (4\omega^2 LC - 1)}.$$

(2.7.3)

If we assume that the entire as passes through the capacitor then  $I_C \approx I_L$  where  $I_C$ and  $I_L$  are alternating currents through C and L respectively. Thus the ac potential across the load (ripple potential) is the potential across the capacitor and is given by

$$V_{rms} = \frac{(I_C)_{rms}}{2\omega C} = \frac{(I_L)_{rms}}{2\omega C} = \frac{4V_0}{3\pi\sqrt{2}(4\omega^2 L C - 1)}$$

$$\therefore \quad Ripple \ factor \ r = \frac{V_{rms}}{V_{dc}} = \left(\frac{4V_0}{3\pi\sqrt{2}(4\omega^2 LC)}\right) l(2V_0 / \pi)$$

$$= 0.47 / (4\omega^2 LC - 1)$$

(2.7.4)

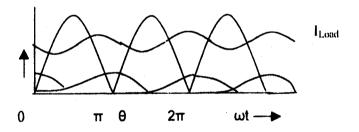

Sine the Inductor filter has low ripple on heavy loads and the capacitor filter has low ripple on light loads, hence it is reasonable to assume that the Inductor input filter has suitable characteristics at all loads. For light loads ( $R_r = \infty$ ), the capacitor charges to the peak voltage with the dc output V<sub>0</sub>. As R<sub>L</sub> is decreased, the diode switches the supply voltage on to the filter and capacitor C is charged to the peak. The dc voltage will be lowered. The diode action is as for the shunt capacitor filter. As the load current is further increased, the discharge of the capacitor is more rapid and the effect of the inductor is appreciable. The upper part of Fig.2.62 shows the variation in V<sub>dc</sub> with I<sub>dc</sub>. Here current I<sub>K</sub> indicates the point at which continuity of load current is obtained and then filter begins to act more like an inductor filter and less a shunt capacitor filter, because of good regulation at the higher load currents. The lower part of Fig.2.62 shows the output current for L-section filter.

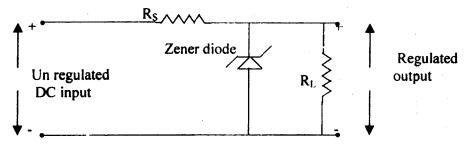

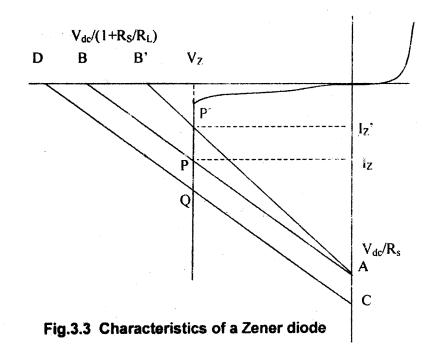

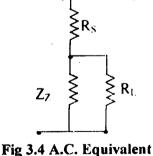

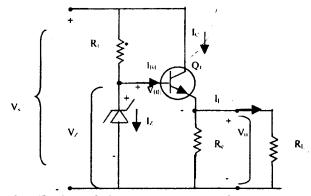

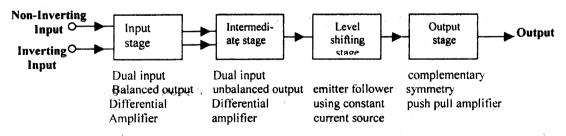

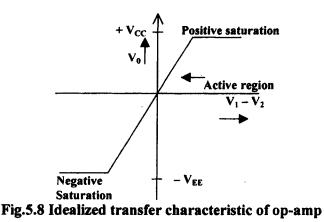

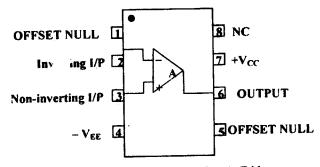

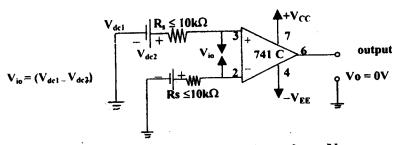

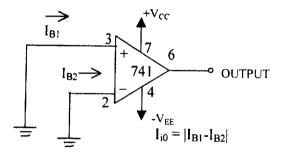

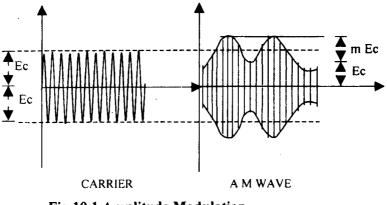

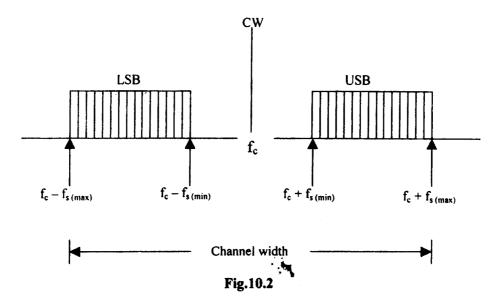

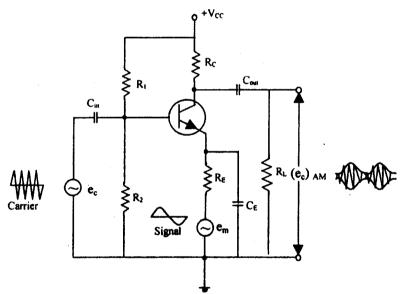

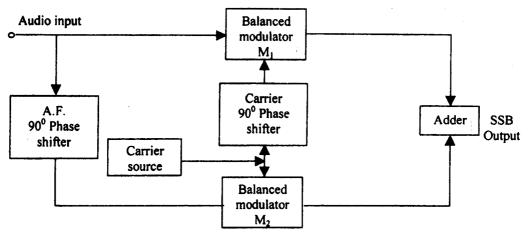

To determine  $I_{K}$ , let us equate the current  $I_{dc}$  and peak-second harmonic current  $I_2$  as